约束衍生时钟

系统中有4个衍生时钟,但其中有两个是MMCM输出的,不需要我们手动约束,因此我们只需要对clk_samp和spi_clk进行约束即可。约束如下:

create_generated_clock -name clk_samp -source [get_pins clk_gen_i0/clk_core_i0/clk_tx] -divide_by 32 [get_pins clk_gen_i0/BUFHCE_clk_samp_i0/O] create_generated_clock -name spi_clk -source [get_pins dac_spi_i0/out_ddr_flop_spi_clk_i0/ODDR_inst/C] -divide_by 1 -invert [get_ports spi_clk_pin]

这里需要注意的是,如果该约束中使用get_pins(即产生的时钟并非输出到管脚),那么无论是source的时钟还是我们衍生的时钟,在get_pins后面的一定是这个时钟最初的产生位置。在视频中我们会具体展示)。

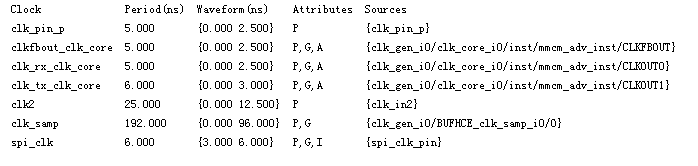

我们再运行report_clocks,显示如下:

我们在理论篇的“create_generated_clock”一节中讲到,我们可以重新设置Vivado自动生成的衍生时钟的名字,这样可以更方便我们后续的使用。按照前文所讲,只需设置name和source参数即可,其中这个source可以直接从report_clocks中得到,因此我们的约束如下:

create_generated_clock -name clk_tx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT1] create_generated_clock -name clk_rx -source [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1] [get_pins clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT0]

大家可以对比下report_clocks的内容和约束指令,很容易就能看出它们之间的关系。

把上述的约束指令在tcl中运行后,我们再运行一遍report_clocks,显示如下:

在时序树的分析中,我们看到,clk_samp和clk2两个异步时钟之间存在数据交互,因此要进行约束,如下:

set_clock_groups -asynchronous -group [get_clocks clk_samp] -group [get_clocks clk2]

本文转自: 科学计算technomania ,作者:猫叔,转载此文目的在于传递更多信息,版权归原作者所有。