1 前言

在上一篇ZCU106 XRT环境搭建【Xilinx Vitis】中,我参考了XRT中其它平台(ZCU102,ZCU104)的Vivado TCL脚本,同时参考了官方的VCU相关工程,编写了ZCU106 XRT的脚本: https://github.com/vacajk/XRT/blob/2019.2/src/platform/zcu106vcu_base/zc...

在这篇文章中将对该工程进行一下分析。

2 Block Design

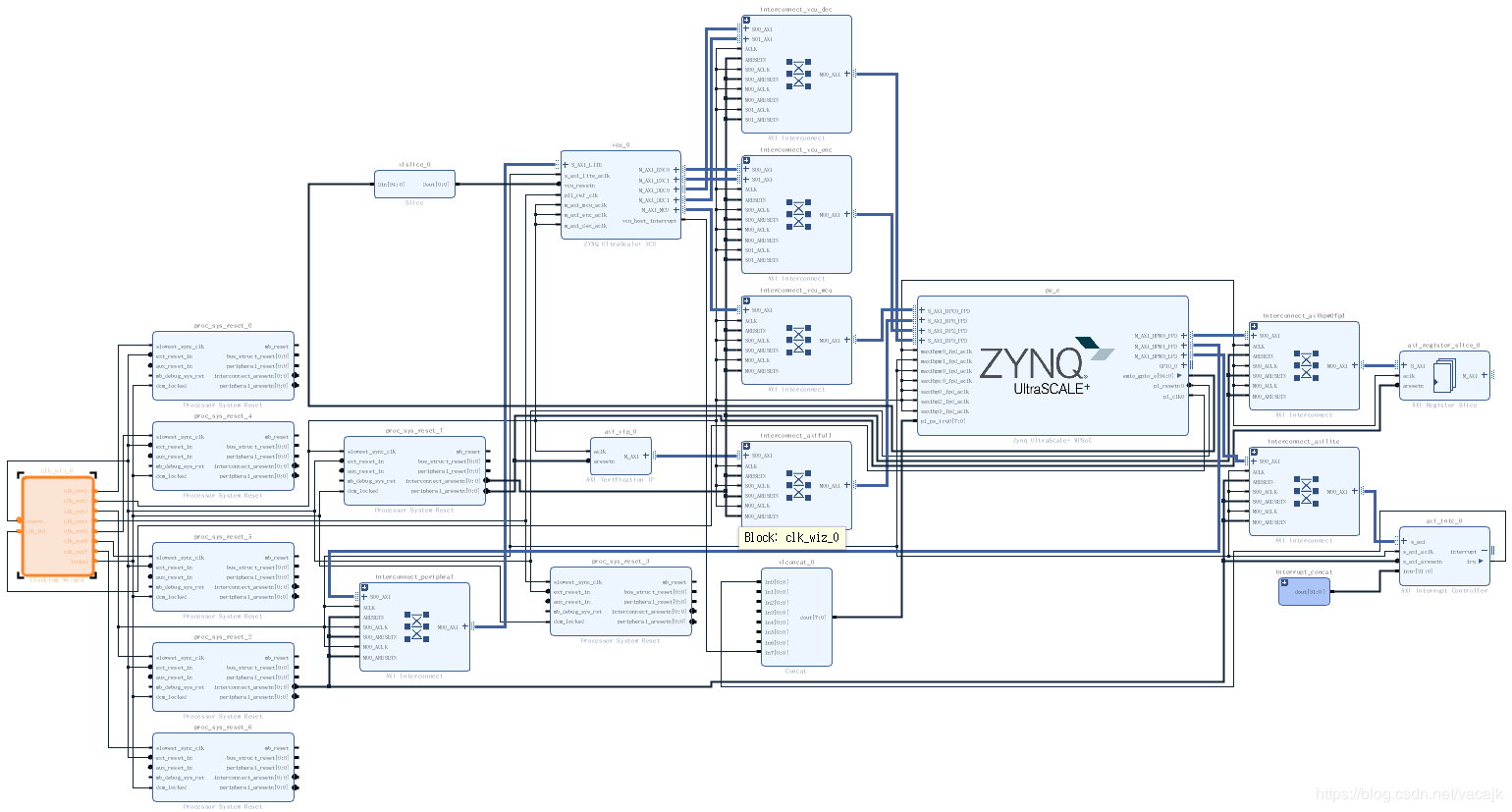

运行 zcu106vcu_base_xsa.tcl 脚本后,会自动生成Vivado工程。打开Vivado后可以查看block design的结构,如下图:

该工程中除了VCU IP是我添加的,其它基本没有什么复杂的IP。都是一些Vitis开发需要的必备结构。

2.1 VCU

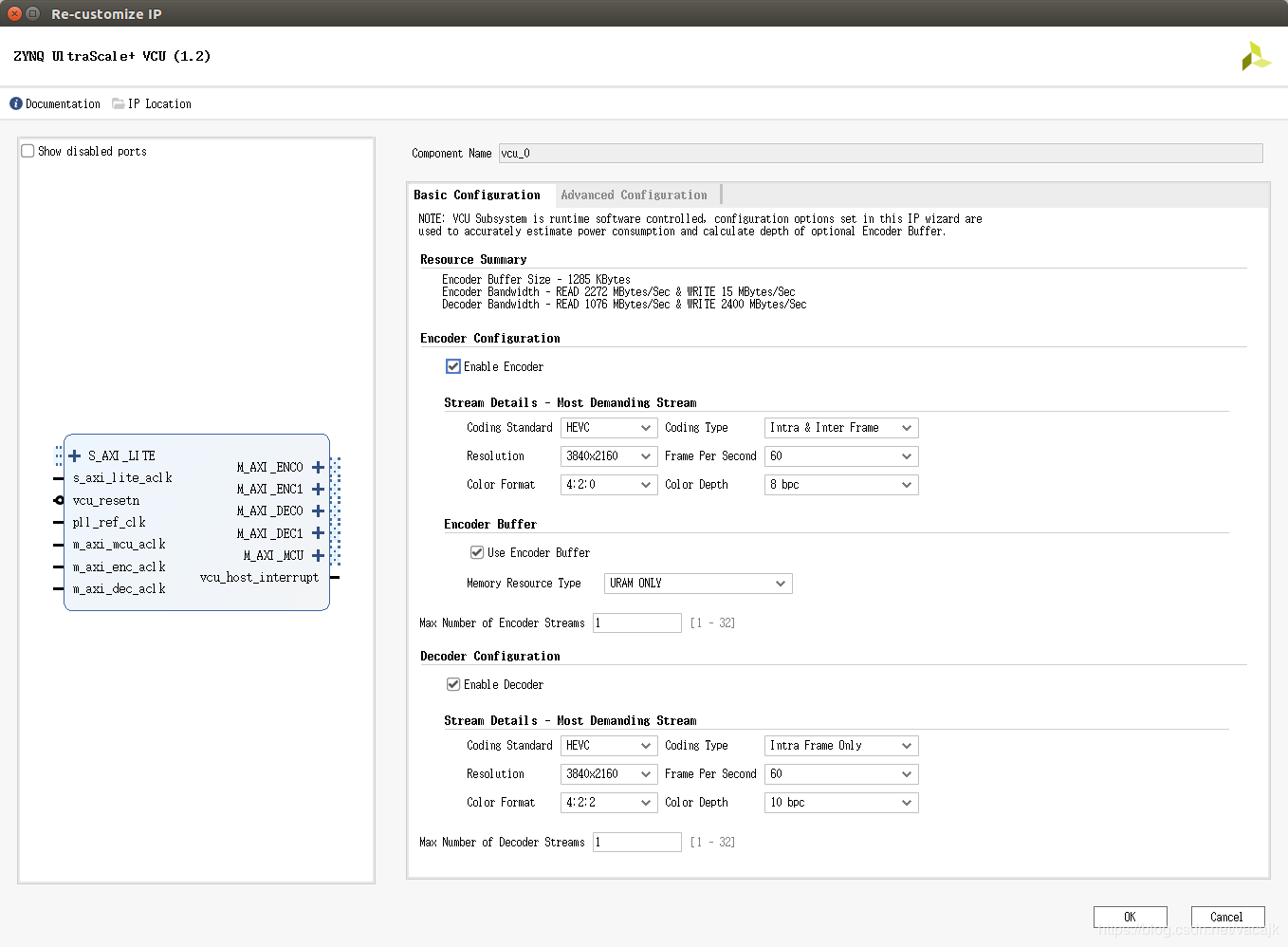

VCU即ZCU*EV系列芯片特有的视频编解码器IP模块。可以实现H264,H265的编解码功能。

VCU的官方文档:pg252vcu

VCU的配置如下,该配置参考的是Xilinx官方的VCU TRD内的IP配置参数。

将来我会开发VCU的相关功能,所以现在先加进来,以后再来使用。VCU的开发本来就是需要基于PetaLinux的,XRT亦是基于PetaLinux的。所以在上一篇博客中的PetaLinux rootfs中同时添加了gstreamer相关的组件。

2.2 Clock

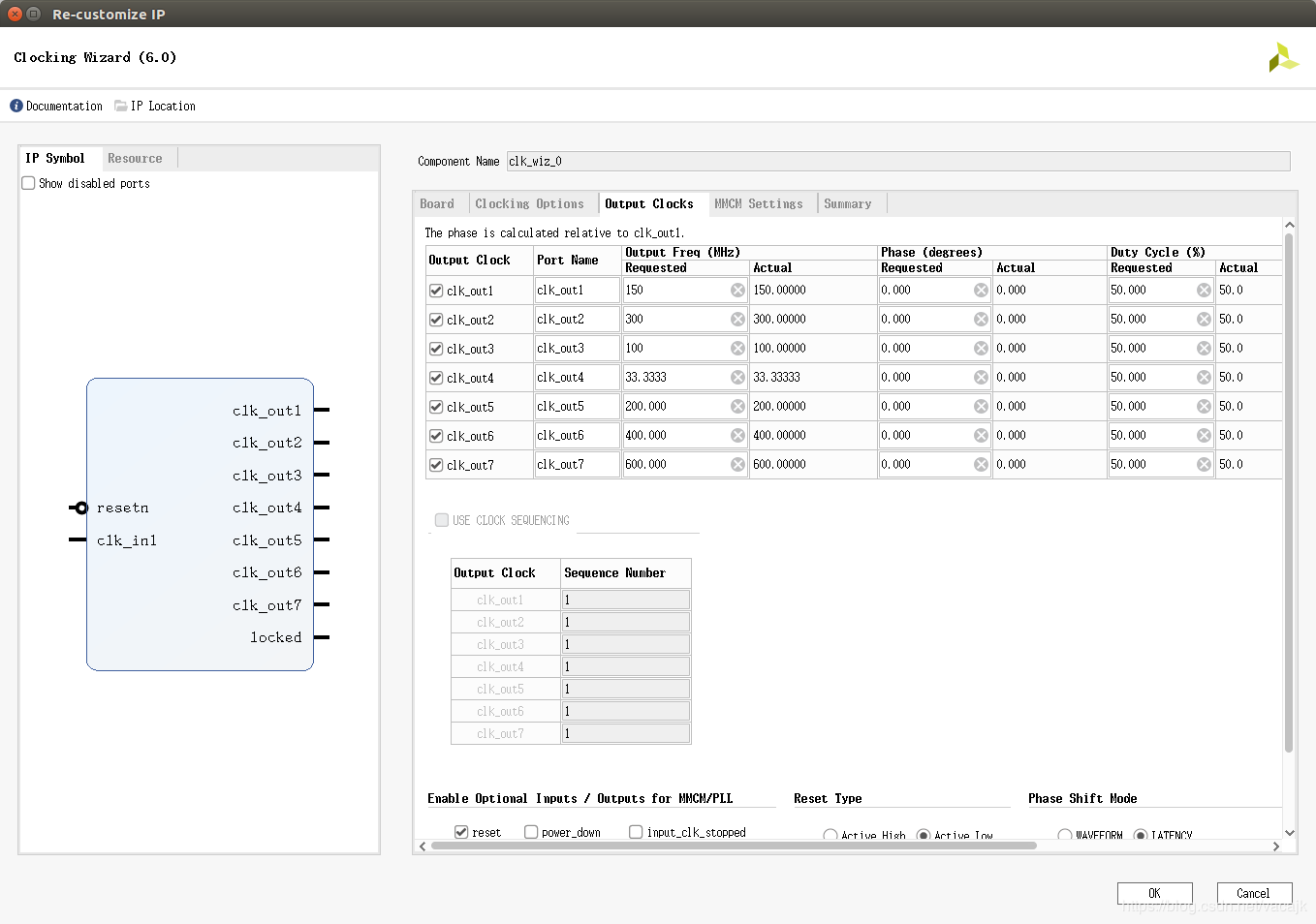

XRT类似与之前的SDSOC,SDACCEL的开发类似,需要预留时钟单元、复位单元等。

为了适配不同的数据处理带宽需求,使用MMCM例化了一组时钟输出,如下图所示。

以上时钟都是参考XRT内的ZCU102和ZCU104的配置,并进行了一些修改。

后续我们常用的时钟一般会选择:150,300,100,200。其它的几个不会太常用,先留在这里。

2.3 ZYNQ PS

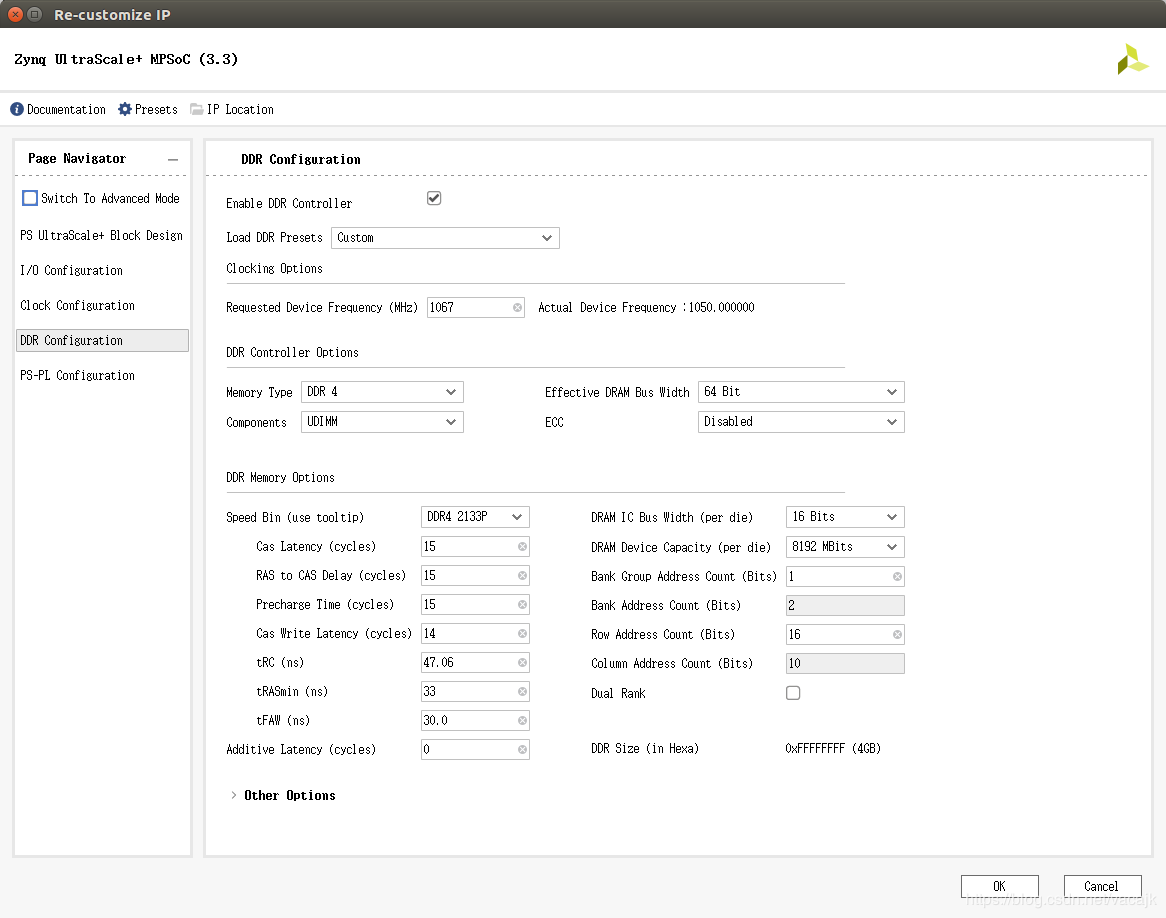

使用了较新的Xilinx ZCU106开发板,上面的DDR4-SODIMM是1RX16类型的(16bit颗粒),所以要修改一下PS的DDR Controller配置,配置如下:(很早时候crazybingo大神告知的,真的省了很多事)

3 编译

在XRT脚本的自动化生成过程中,并未对该工程进行综合和实现,而是直接在创建好block design后直接生成xsa来使用的。所以我们也不需要进行编译了,后面在Vitis的硬件加速编译过程中会自动添加相关加速RTL,以及进行Vivado工程综合的。

4 其它

预留位置,后续有其它RTL更新后我会回过头来更新这篇文章的内容。目前来看,添加了VCU IP后,基本是够用了。

————————————————

版权声明:本文为CSDN博主「vacajk」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/vacajk/article/details/103542739