作者:Hong Han,来源: 赛灵思中文社区论坛

注意:本论坛博客所有内容皆来源于Xilinx工程师,如需转载,请写明出处作者及赛灵思论坛链接并发邮件èï¼æªç»Xilinxåèä½æ人许å¯ï¼ç¦æ¢ç¨ä½åä¸ç¨é

ææ¶æ们éè¦å¨è®¾è®¡ç½è¡¨çåºç¡ä¸å¾®è°ä¸ä¸é»è¾ï¼è¿æ ·å¯ä»¥æ éä¿®æ¹ä»£ç ï¼ä¹æ ééæ°å综åï¼å¨è®¾è®¡è°è¯ä¸å¯ä»¥èçæ¶é´åæ¶ç»´æå ¶ä»é»è¾æ ä»»ä½æ¹å¨.

è¿é带大家ä¸èµ·ä½éªä¸ä¸Vivado çECOæµç¨ï¼ä»¥vivadoèªå¸¦çExample Design为ä¾, ç´æ¥ç¨TCLå½ä»¤ä¿®æ¹ç½è¡¨ï¼å¨æ£å¸¸çå¯åå¨è·¯å¾ä¹é´å ä¸çº§LUT.

1. æå¼Vivado çé¢

2. æå¼Example Design "Wavegen":

<1> File -> Project -> Open Example

<2> éä¸Wavegen(HDL), å¨ä»¶éæ©xcku035

3. ç¹å»å·¦ä¾§Flow Navigator çªå£ Run Implementation æé®, å®æ综åå®ç°.

4. æå¼Implemented Design ï¼ç¹å»å·¦ä¾§Flow Navigator çªå£ Open Implemented Design æé®ï¼

5. éä¸æ¡ä¸¤ä¸ªå¯åå¨ä¹é´çè·¯å¾

è¿è¡ä»¥ä¸å½ä»¤ï¼éä¸æå°åºçè·¯å¾ï¼åå»å¯ä»¥æ¥çæ¶åºæ¥åï¼F4 é®å¯ä»¥æå¼è¿æ¡è·¯å¾çåçå¾

%report_timing -from [get_cells clkx_spd_i0/meta_harden_bus_new_i0/signal_meta_reg] -to [get_cells clkx_spd_i0/meta_harden_bus_new_i0/signal_dst_reg] -delay_type max -name test1

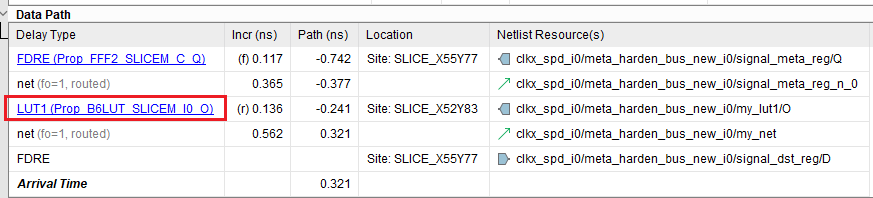

å¯ä»¥çå°Data Pathçå¸çº¿å»¶è¿æ¯0.504ns

è·¯å¾çåçå¾

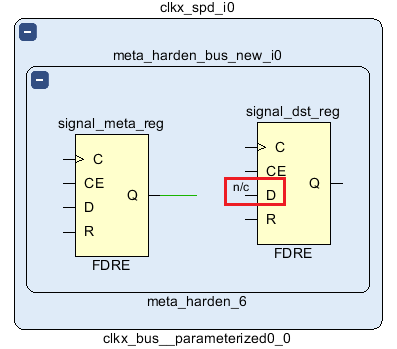

6. æç®çå¯åå¨çD端ä»netä¸æä¸æ¥

%disconnect_net -net

clkx_spd_i0/meta_harden_bus_new_i0/signal_meta_reg_n_0 -objects

{clkx_spd_i0/meta_harden_bus_new_i0/signal_dst_reg/D}

å¨è¿éè·åæä½å¯¹è±¡(net, Pin) çæ¹æ³: å¨åçå¾ä¸éä¸å¯¹è±¡ï¼ç¶åæ¥çèµ°ä¸è§Property çªå£ä¸çNAME å±æ§

Pin被ä»Netä¸æå¼åï¼ä¼å¨åçå¾ä¸æ¾ç¤ºn/c

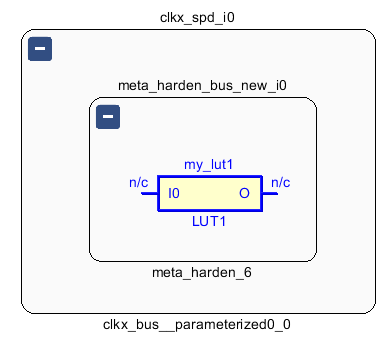

7. å建ä¸ä¸ªLUT1ï¼å¹¶è®¾ç½®LUTçINIT property

%create_cell -reference LUT1clkx_spd_i0/meta_harden_bus_new_i0/my_lut1 %set_property INIT 2'h1 [get_cells clkx_spd_i0/meta_harden_bus_new_i0/my_lut1]

å¯ä»¥çå°è¿ä¸ªæ°å建çLUT1ææ端å£(Pin)é½æ¯æ¬ç©ºç. æ¥ä¸æ¥çæ¥éª¤è¦å°è¿äºpinè¿æ¥å°åéçnetä¸.

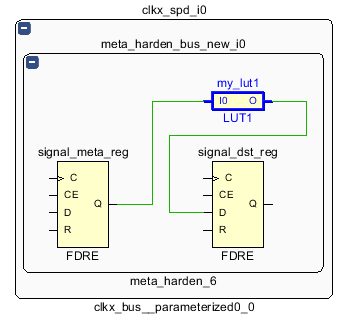

8. æLUT1çè¾å ¥ç«¯å£è¿æ¥å°ä¹åæå¼çnetä¸.

%connect_net -net clkx_spd_i0/meta_harden_bus_new_i0/signal_meta_reg_n_0 -objects {clkx_spd_i0/meta_harden_bus_new_i0/my_lut1/I0}

9. å建ä¸ä¸ªæ°çnetç¨æ¥è¿æ¥LUT1çè¾åºpinåä¹åæä¸æ¥çå¯åå¨D pin

%create_net clkx_spd_i0/meta_harden_bus_new_i0/my_net

10. è¿æ¥LUT1çè¾åºpinåä¹åæä¸æ¥çå¯åå¨D pin å°æ°å建çnetä¸

%connect_net -net clkx_spd_i0/meta_harden_bus_new_i0/my_net -objects {clkx_spd_i0/meta_harden_bus_new_i0/my_lut1/O clkx_spd_i0/meta_harden_bus_new_i0/signal_dst_reg/D}

11. å¨Netlistçªå£éçªå£éä¸æ°å»ºçLUT1ï¼å°å ¶ææ³å°Deviceä¸ç©ºççslice LUT belä¸

对åºçå½ä»¤:

place_cell clkx_spd_i0/meta_harden_bus_new_i0/my_lut1 SLICE_X52Y83/B6LUT

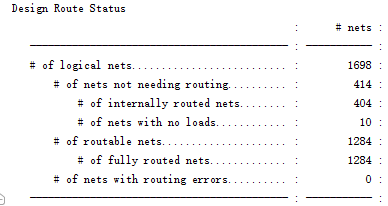

12. 对æ°çLUT1两端çnetè¿è¡å¸çº¿

%route_design -nets [get_nets -of [get_pins clkx_spd_i0/meta_harden_bus_new_i0/my_lut1/*]]

13.æ£æ¥å¸çº¿ç»æç¡®ä¿æ²¡æå¸çº¿é误

%report_route_status

14.ç¨æ¥éª¤5çå½ä»¤éæ°æ¥ä¸ä¸æ¶åº

15. çæbitæ件

%write_bitstream test.bit