描述

当使用 Dynamic Function eXchange(部分重新配置)流程时,该工具报告显示成功生成了比特流,没有 DRC 错误,但生成的部分比特流不正确。

部分比特流下载后,时钟停止运行。

解决方案

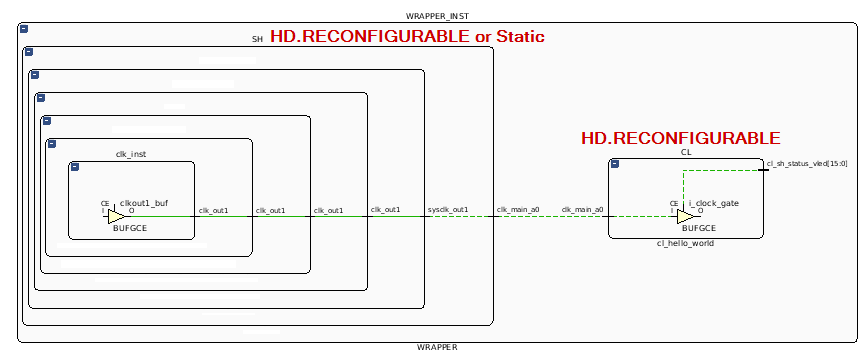

下面所显示的网表结构会在 Vivado 2019.1 中导致该问题。请注意,一个分区 (SH) 中的一个 BUFGCE 正在驱动另一个分区 (CL) 中的一个 BUFGCE。

虽然在特定网表中,SH 和 CL 是可重新配置的模块,但是级联 BUFG 也不允许从静态模块到可重新配置的模块。

出现这种行为的原因

问题的根源是,部分比特流的路由足迹不包括从静态或可重配置模块中的第一个 BUFG(上述网表中的 SH)到另一个可重配置模块中的第二个 BUFG(上述网表中的 CL)的时钟网络。

时钟网络也没有使用预期的分区引脚 LOC (PPLOC)。

虽然 Vivado 确实提供了内部 HD 路由后 DRC 来捕获这种违规,但它没有为这个网表结构做标记。

解决方案

请按照以下的一个建议操作,避免跨 DFX 单元边界使用级联 BUFGCE。

Vivado 将引入一个前置 DRC 来为 2020.1 标记这种违规网表。

选项 1:

如果时钟不需要在 CL 区域内修改或选通,则删除级联的全局缓冲区。

第一个缓冲区(在 SH 层级中)将足以驱动全局逻辑。

选项 2:

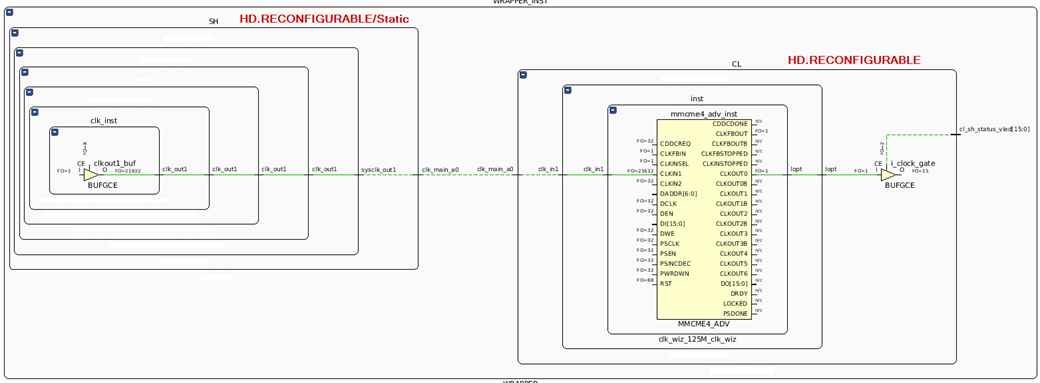

请修改时钟结构,将 MMCM/ PLL 用作两个 BUFGCE 间的桥接器。

该 MMCM/PLL 可以位于两个分区中的任何一个中。

下面是更新的网表视图,提供有推荐的时钟结构。

选项 3:

您还可将架构资源 (LUT/FF) 用作两个 BUFGCE 间的桥接器。

但这是最不可取的选项,因为将时钟轨道卸载到架构资源,会导致严重偏移。