使用 Vitis 软件平台进行加速流程应用开发

Vitis™统一软件平台工具将赛灵思软件开发的方方面面全部组合到统一的环境内。Vitis软件平台支持Vitis嵌入式软件开发流程以满足希望迁移至下一代技术的赛灵思软件开发套件 (SDK) 用户的使用需求,也支持 Vitis 应用加速开发流程,以满足希望使用基于赛灵思 FPGA 的最新软件加速功能的软件开发者的需求。此处内容主要与应用加速流程以及Vitis 核开发套件和赛灵思的 Xilinx Runtime (XRT) 的使用有关。

Vitis 应用加速开发流程提供了相应的框架,可通过使用标准编程语言来为软件和硬件组件开发和交付 FPGA 加速应用。软件组件或主机程序是使用 C/C++ 语言开发的,可在 x86 或嵌入式处理器上运行,借助 OpenCL™ API 调用来管理与加速器的运行时交互。硬件组件或内核则可使用C/C++、OpenCL C或RTL来开发。Vitis软件平台有助于促进对异构应用的硬件和软件元素进行并发开发和测试。

图 1:Vitis 统一软件平台

如上图所示,Vitis统一软件平台由以下功能特性和元素组成:

•以加速硬件平台为目标的Vitis技术(例如,Alveo™数据中心加速器卡)和基于Versal®或Zynq® UltraScale+™MPSoC 的嵌入式处理器平台。

• XRT 可提供 API 和驱动程序,以供您的主机程序用于连接到目标平台,并处理您的主机程序与加速内核之间的传输事务。

Vitis 核开发套件可以提供软件开发工具堆栈(例如,编译器和交叉编译器)、分析器以及调试器,开发工具可用于构建主机程序和内核代码,分析器供您用于对应用性能进行剖析和分析,调试器则可帮助您定位和修复应用中的任何问题。

Vitis 加速库可提供性能优化的 FPGA 加速,仅需最低限度的代码更改,且无需重新实现算法即可充分发挥赛灵思自适应计算的所有优势。Vitis加速库可用于常用数学、统计数据、线性代数和DSP的常用函数,并且可用于特定领域的应用,例如,视觉和图像处理、计量金融、数据库、数据分析以及数据压缩等。如需了解有关 Vitis 加速库的更多信息,请访问 https://xilinx.github.io/Vitis_Libraries/。

FPGA 加速

相比传统 CPU/GPU 加速,赛灵思 FPGA 可提供诸多优势,包括能够实现可在处理器上运行的任意功能的定制架构,可以更低的功耗损耗实现更高的性能。相比于处理器架构,赛灵思器件中由可编程逻辑 (PL) 互连结构所构成的结构在应用执行中可支持实现高度并行性。

为了在赛灵思器件上实现软件加速的优势,您应想方设法将加速目标设定为硬件中的应用程序内存在密集计算的各部分。在定制硬件上实现这些功能即可帮助您在性能与功耗之间达到理想平衡。

如需了解有关如何设计硬件架构以实现最优性能的更多信息,以及有关其它设计技巧建议的信息,请回顾 使用 Vitis 软件平台加速应用的方法论。

执行模型

在 Vitis 核开发套件中,应用程序被分为主机应用部分和硬件加速内核部分,并在这两部分之间建立通信通道。以 C/C++语言编写且使用API抽象(如OpenCL)的主机程序会编译为在主机处理器(例如,x86服务器或用于嵌入式平台的 Arm 处理器)上运行的可执行文件,而硬件加速内核则会编译为在赛灵思器件的可编程逻辑 (PL) 区域内运行的可执行器件二进制文件 (.xclbin)。

由 XRT 管理的 API 调用用于处理主机程序与硬件加速器之间的传输事务。主机与内核之间的通信(包括控制和数据传输)都会跨 PCIe® 总线或 AXI 总线(针对嵌入式平台)发生。在硬件中的特定存储器位置之间传输控制信息时,使用全局存储器在主机程序与内核之间进行数据传输。主机处理器和硬件加速器均可访问全局存储器,但仅限主机应用才能访问主机存储器。

例如,在典型应用中,主机首先将内核要操作的数据从主机存储器传输到全局存储器中。随后,内核对此数据进行操作,并将结果存储回全局存储器。内核完成操作后,主机会将结果传回主机存储器。主机与全局存储器之间的数据传输会引发时延,这可能牺牲总体应用性能。为了在真实系统中实现加速,硬件加速内核带来的优势必须大于数据传输所添加的时延。

目标平台包含 FPGA 加速内核、全局存储器和直接存储器访问 (DMA) 用于执行存储器传输。内核可以拥有一个或多个全局存储器接口,并且可编程。Vitis核开发套件执行模型可分解为以下步骤:

1. 主机程序将内核所需的数据写入已连接的器件的全局存储器,此器件可通过 Alveo 数据中心加速器卡上的 PCIe 接口或者嵌入式平台上的 AXI 总线来连接。

2. 主机程序使用其输入参数来设置内核。

3. 主机程序在 FPGA 上触发内核函数的执行。

4. 必要时,内核在从全局存储器中读取数据时执行所需的计算。

5. 内核将数据写回全局存储器并通知主机它已完成任务。

6. 主机程序将数据从全局存储器读回主机存储器,并根据需要继续处理。

FPGA可以在加速器上容纳多个内核实例,包括不同类型的多个内核和相同内核的多个实例。XRT以用户不可知方式统筹安排加速器内主机程序与内核之间的交互。如需获取 XRT 架构文档,请访问 https://xilinx.github.io/XRT/。

数据中心应用加速开发流程

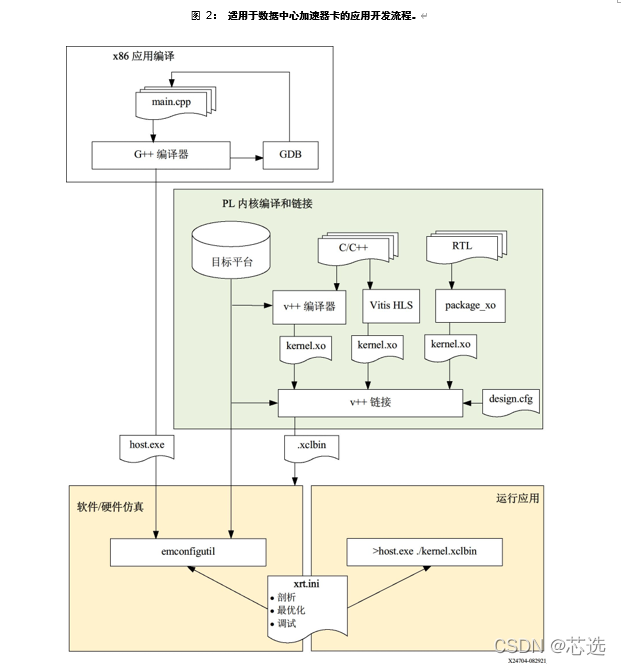

下图描述了构建和运行应用以供在 Alveo 数据中心加速器卡上使用所需的步骤。这些步骤总结如下,在这整篇文档中均可找到有关每个步骤的详细信息。

图 2:适用于数据中心加速器卡的应用开发流程。

x86 应用编译:编译主机应用以供在 x86 处理器上运行,该处理器使用 G++ 编译器来创建主机可执行文件。该主机程序可与 PL 区域中的内核进行交互。如需了解有关写入主机应用的更多信息,请参阅 第二部分:开发应用。如需了解有关编译主机应用的更多信息,请参阅 构建主机程序。

PL内核编译和链接:PL内核经编译后即可在目标平台的PL区域内实现。PL内核可编译到赛灵思对象格式(XO)文件中,编译可使用Vitis编译器(v + +)、Vitis HLS (适用于C/C++内核)或package_xo命令(适用于RTL内核)来执行。如需了解有关内核编码的信息,请参阅 C/C++ 内核 或 RTL 内核。

Vitis编译器还会将内核XO文件与硬件平台相链接,从而为应用创建器件可执行文件(.xclbin)。如需了解更多信息,请参阅 构建器件二进制文件。

赛灵思对象(XO)文件通过v + + --link命令与目标硬件平台相链接,以创建器件二进制文件(.xclbin),此文件将被加载到目标平台上的赛灵思器件中。

运行应用:对于Alveo数据中心加速器卡,.xclbin文件是运行系统所必需的构建对象。运行应用时,可以运行软件仿真、硬件仿真或者在实际物理加速器平台上运行。如需了解更多信息,请参阅 运行应用硬件构建。

•当构建目标为软件或硬件仿真时,emconfigutil命令可构建目标平台的仿真模型。Vitis编译器会在器件二进制文件中生成内核的仿真 (simulation) 模型,运行此应用则会运行系统的此模型。如 构建目标 中所述,仿真(emulation) 目标允许您在相对较快的周期内对设计进行构建、运行和迭代,并进行应用调试和性能评估。

•当构建目标为硬件系统时,目标平台是物理器件。Vitis编译器会使用Vivado Design Suite生成.xclbin来运行综合与实现,并解决时序。运行应用会在硬件上运行系统。构建进程将自动执行以生成高质量的结果。但熟悉硬件的开发者可以在其设计进程中充分利用 Vivado 工具。

嵌入式处理器应用加速开发流程

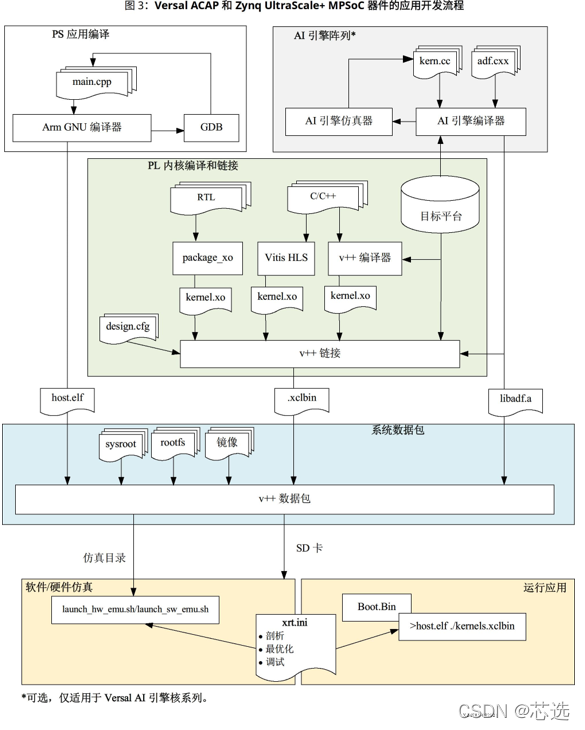

下图描述了使用 Arm® 处理器和内核构建和运行应用所需的步骤,这些处理器和内核在 Versal ACAP、Zynq UltraScale+ MPSoC 和 Zynq-7000 SoC 器件的可编程逻辑区域内运行。这些步骤总结如下,在这整篇文档中均可找到有关每个步骤的详细信息。

X24705-082921

PS 应用编译:编译主机应用以在 Cortex®-A72 或 Cortex-A53 核处理器上运行,此类处理器使用 GNU Arm 交叉编译器来创建 ELF 文件。主机程序会与器件的 PL 和 AI 引擎区域中的内核进行交互。如需了解有关写入主机应用的更多信息,请参阅 第二部分:开发应用。如需了解有关编译主机应用的更多信息,请参阅 构建主机程序。

AI 引擎阵列(可选,仅供 Versal AI 引擎 Core 系列使用):部分 Versal ACAP 器件将超长指令字 (VLIW) 处理器的AI引擎阵列与单指令流多数据流⑸MD)矢量单元整合在一起,后者专为计算密集型应用(例如,5G无线和人工智能(AI)应用)而经过高度优化。AI引擎Graph和内核是使用Vitis工具(例如, aiecompiler 和aiesimulator)构建的,可集成到嵌入式加速器应用加速流程中,如《Versal ACAP AI引擎编程环境用户指南》(UG1076) 中所述。

PL内核编译和链接:PL内核经编译后即可在目标平台的PL区域内实现。PL内核可使用Vitis编译器(v++)、VitisHLS (针对C/C++内核)或package_xo命令(针对RTL内核)编译为赛灵思对象格式(XO)文件。如需了解有关内核编码的更多信息,请参阅 C/C++ 内核 或 RTL 内核。

Vitis编译器还会将内核XO文件与硬件平台相链接,从而为应用创建器件可执行文件(.xclbin)。如需了解更多信息,请参阅 构建器件二进制文件。

赛灵思对象(XO)文件通过v + + --link命令与目标硬件平台相链接,以创建器件二进制文件(.xclbin),此文件将被加载到目标平台上的赛灵思器件中。

系统封装:v++ --package命令可用于收集配置和启动系统以及加载和运行应用(包括主机应用和PL内核二进制文件)所需的文件。此步骤会构建必要的封装以运行软件或硬件仿真和调试,或者创建 SD 卡以在硬件上运行您的应用。如需了解更多信息,请参阅 封装系统。

运行应用:运行应用时,可以运行软件仿真、硬件仿真或者在实际物理加速器平台上运行。在嵌入式处理器平台上运行应用与在数据中心加速器卡上运行应用不同。如需了解更多信息,请参阅 运行应用硬件构建。

•当构建目标为软件或硬件仿真时,QEMU环境会对硬件器件进行建模。Vitis编译器会在器件二进制文件中生成内核的仿真 (simulation) 模型,运行应用则会在系统的 QEMU 模型中运行。如 构建目标 中所述,仿真(emulation) 目标允许您在相对较快的周期内对设计进行构建、运行和迭代,并进行应用调试和性能评估。

•当构建目标为硬件系统时,目标平台是物理器件。Vitis编译器会使用Vivado Design Suite生成.xcibin来运行综合与实现,并解决时序。运行应用会在硬件上运行系统。构建进程将自动执行以生成高质量的结果,但熟悉硬件的开发者可以在其设计进程中充分利用 Vivado 工具。

构建目标

Vitis编译器构建进程会生成主机程序可执行文件和FPGA二进制文件(.xclbin)。FPGA二进制文件的性质是由构建目标确定的。

当构建目标为软件或硬件仿真(emulation)时,Vitis编译器会在FPGA二进制文件中生成内核的仿真(simulation)模型。这些仿真 (emulation) 目标允许您在相对较快的周期内构建、运行和迭代设计、调试应用并评估性能。

当构建目标为硬件系统时,Vitis编译器会为硬件加速器生成.xcibin,并使用Vivado Design Suite来运行综合与实现。它使用这些工具和预定义、经验证的设置来提供理想的结果质量。使用 Vitis 核开发套件不需要具备这些工具的知识;但是,熟悉硬件的开发者可以充分利用这些工具并使用所有可用功能特性来实现内核。

Vitis 编译器提供了 3 个不同的构建目标,其中 2 个仿真目标用于调试和确认目的,而默认硬件目标则用于生成实际的FPGA 二进制文件:

软件仿真(sw_emu):主机应用代码和内核代码均编译为在主机处理器上运行。这样即可通过快速构建并运行(fastbuild-and-run) 循环来实现迭代算法优化。此目标可用于确定语法错误、执行与应用程序一起运行的内核代码的源代码级调试,以及验证系统行为。

硬件仿真(hw_emu):内核代码编译到硬件模型(RTL)中,此模型在专用仿真器内运行。此构建和运行循环需要更长时间,但是提供详细的、周期精确的内核活动视图。此目标用于测试逻辑的功能,该逻辑将引入 FPGA 用于获取初始性能估算。

硬件(hw):内核代码编译到硬件模型(RTL)中,然后在FPGA上实现,从而生成将在实际FPGA上运行的二进制文件。

教程与示例

为帮助您快速开始使用 Vitis 核开发套件,您可在 https://github.com/xilinx/Vitis-Tutorials 上的以下仓库中查找教程、应用示例以及硬件内核。

Vitis 应用加速开发流程教程:提供多种教程,通过这些教程可以教授有关工具流程和应用开发的具体概念。

入门路径教程最适合新用户入门。

Vitis 示例:包含许多示例,用于演示良好的设计实践、编码指南、常用应用的设计模式以及(最重要的)最优化技巧,从而最大程度提升应用性能。板载示例分为几种主要类别。每种类别都具有多种关键概念,采用适用的OpenCL™ C 和 C/C++ 框架通过各不同示例来展示。所有示例都包含 Makefile 以支持软硬件仿真并在硬件上运行,还包含 README.md 文件,其中具有示例的详细解释。

现在您已掌握了 Vitis 核开发套件的各要素,并且已经了解了如何为加速编写和构建应用,下一步,让我们来回顾下解决您的设计问题的最佳方法。

本文转载自:芯选