作者:米联客(milianke)

软件版本:vitis2021.1(vivado2021.1)

操作系统:WIN10 64bit

硬件平台:适用AMD-XILINX A7/K7/Z7/ZU/KU系列FPGA

1 概述

仿真是每个初学者必须学会的一项技能,因为FPGA程序编译时间往往很长,所以对程序进行仿真就成为了校验程序正确性的最快捷的方式。

本节课,我们将通过Modelsim以及vivado两个不同软件,使用两种方法对我们上节课所生成的程序进行仿真,带读者快速掌握基本的FPGA开发技能。

2使用vivado进行仿真

相比较Modelsim仿真,我们直接使用vivado进行仿真就显得简单得多,仅仅只需要编辑好我们的Test Bench,也就是我们俗称的TB文件就可以了。

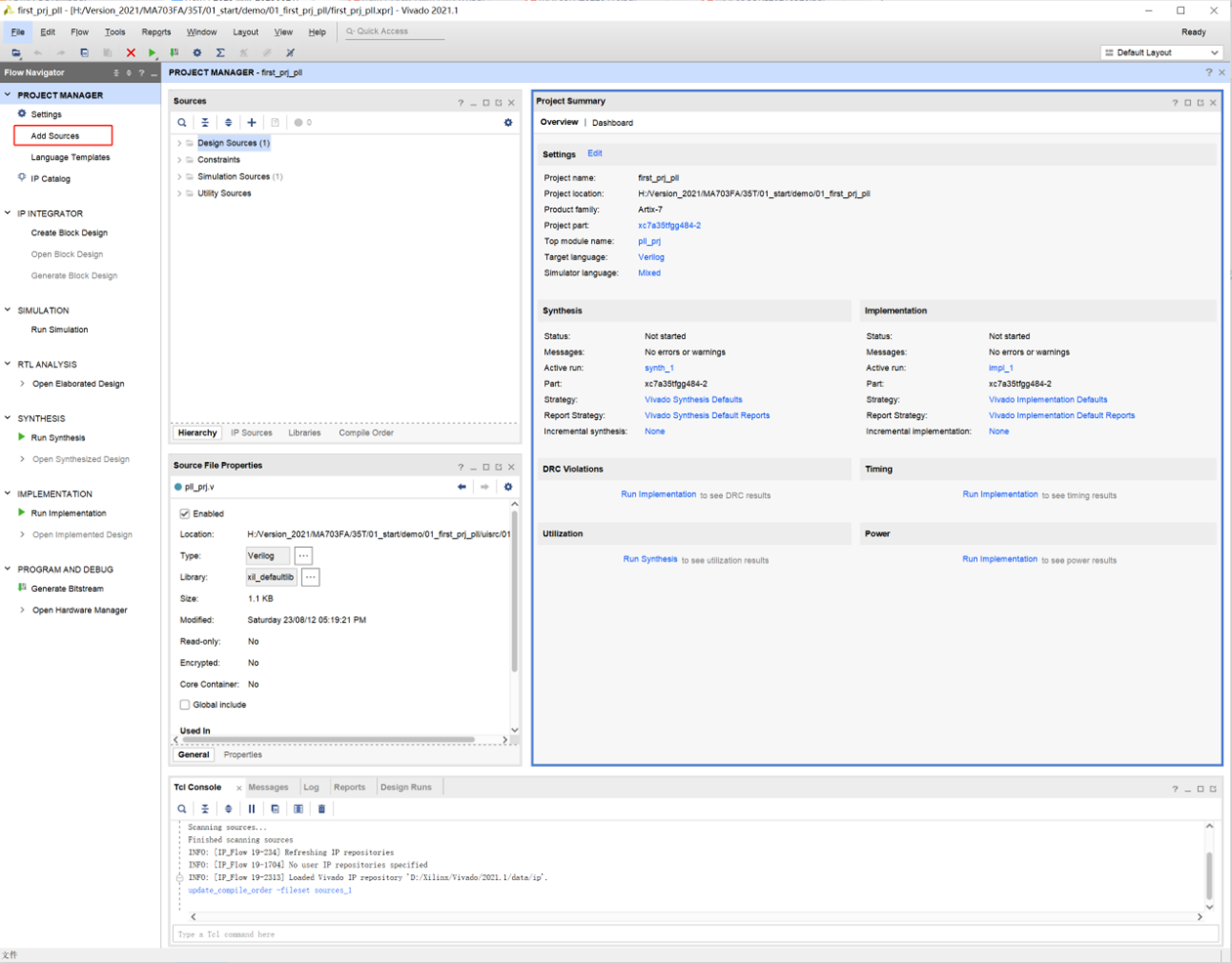

2.1添加RTL仿真文件

首先我们打开上一节课做的程序,添加RTL文件。添加RTL文件的方法跟添加verilog文件的文件方法类似

Step1:单击 Add Sources

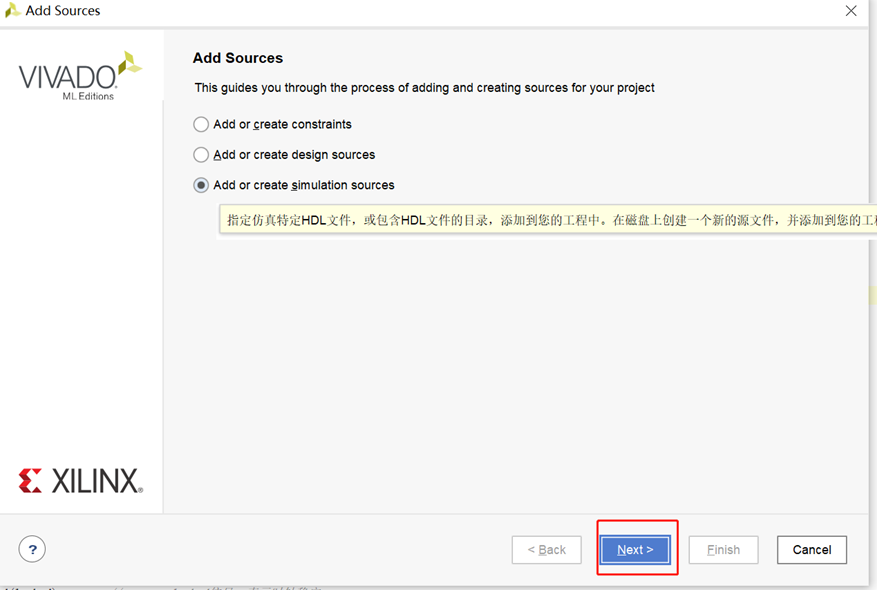

Step2:选择需要添加的文件类型,这里我们选择仿真类型的文件,点击Next添加确定

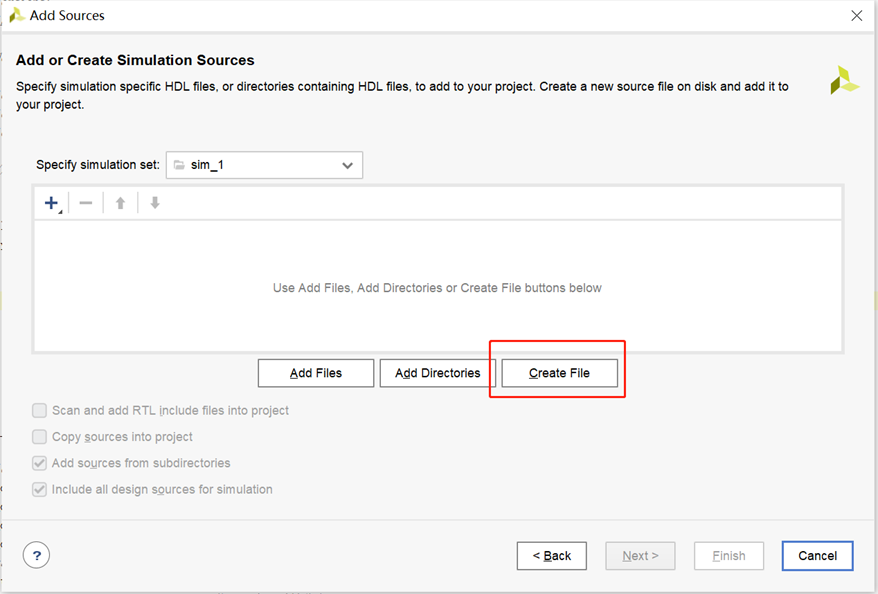

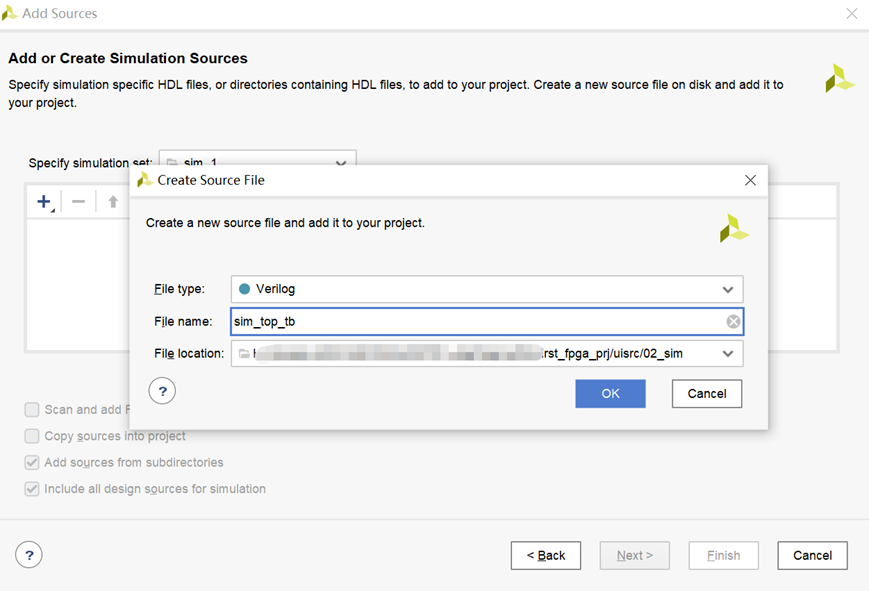

Step3:点击Create File创建一个新的Test Bench文件,当然,如果你有提前写好的TB文件也可以直接点Add Files添加已有的文件。

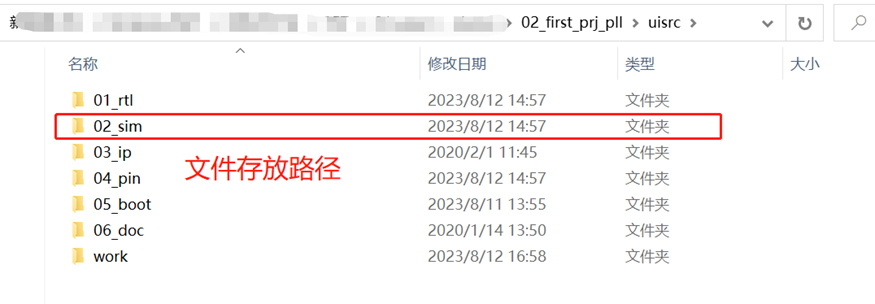

Step4:创建一个pll_test_TB的文件,并且文件类型选择Verilog,路径可以选择存放在工程默认路径下,米联客推荐存放在创建的FPGA工程目录的uisrc\02_sim目录下,方便管理,注意整个路径不允许出现中文。

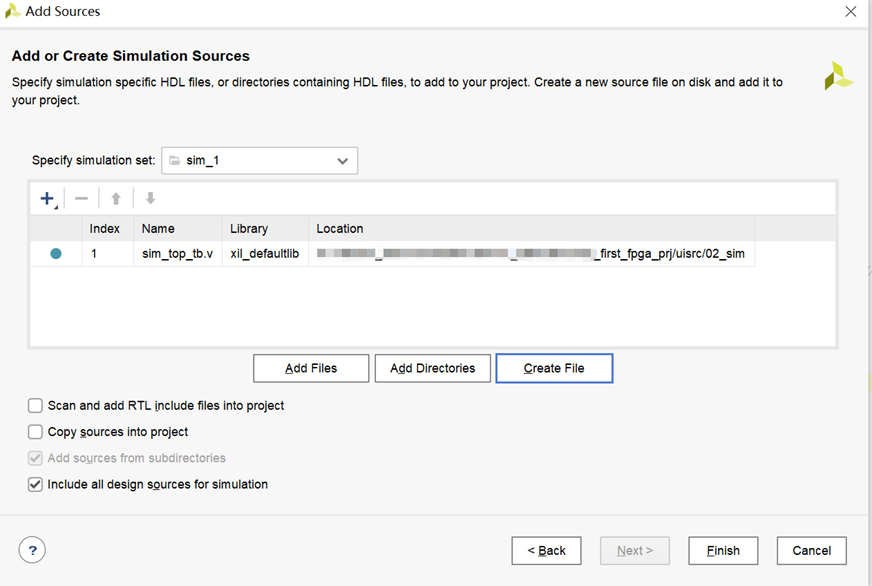

Step5:点击OK确认生成文件,点击Finsh结束

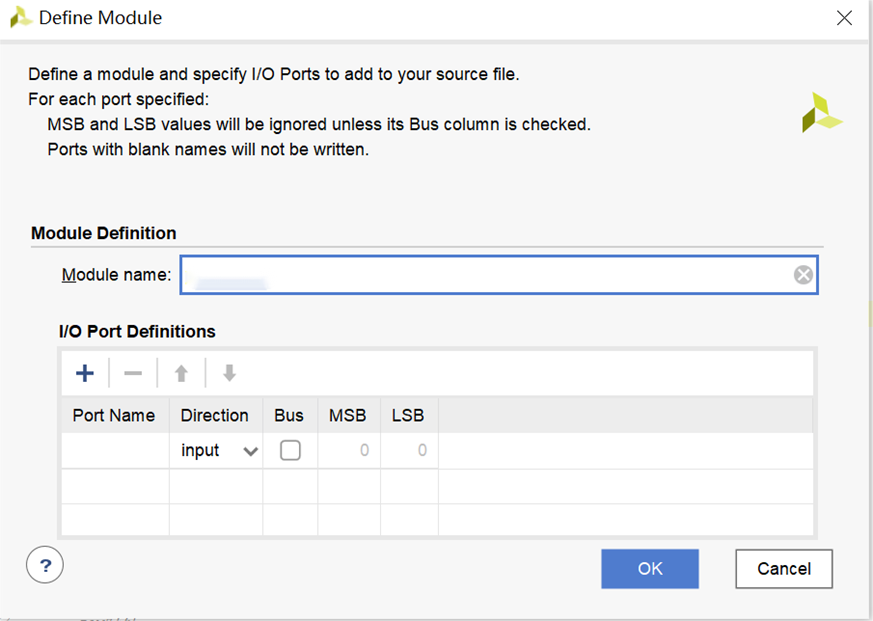

Step6:这边可以预先添加端口以及修改模块名,我们保持默认,直接点击OK即可。

Step7:这边我们的TB文件就新建完成了,但是我们发现他跟我们的主程序"pll_test.v"是保持平行状态的。那是因为我们的TB文件里面内容为空,所以并不对我们的主程序有任何激励,也同样没有对我们的主模块进行例化,所以我们接下来就是要进行例化操作。

2.2编写RTL仿真文件

首先我们要有一个概念,我们仿真的目的是模拟代码实际运行时候的一个状态。所以我们要做的就是尽可能真实的还原我们将程序下载后,我们实际开发板的运行状态。然后使用例化的方式,将我们的信号接入我们的主程序模块,方法类似我们例化IP,所以例化的部分我们不详细讲解。

我们目前的代码比较简单,由于我们的使用的开发板的系统时钟是50M,所以我们仅仅需要模拟一个50M的系统时钟即可。

本教程具有通用性,可作为其他型号的FPGA参考学习资料,如果作为其他型号的FPGA参考使用,开发板的系统时钟存在差异,请在理解原理后适当修改,切勿生搬硬套。

由于时钟翻转我们需要保持高/低电平的状态,所以我们设置一个reg类型的寄存器"clk_i",然后使该寄存器定时翻转。

这边我们使用一个关键词"`timescale"来控制我们仿真的精度,我们本次模拟的是一个50M的时钟,我们的周期为20ns,所以我们设置每10ns进行一次翻转,我们的仿真精度是1ns,所以我们翻装的周期设置"#10",我们具体代码如下

`timescale 1 ns/100ps

module sim_top_tb;

reg sysclk; //时钟信号

wire [1:0] up_led; //仿真的LED 信号

pll_test u_pll_test(

.I_sysclk_p(sysclk),

.O_up_led(up_led)

);

initial

begin

sysclk = 1'b0;

end

///////////////////////////////////////////////////////////////////

//

// Clock generation

//

always #10 sysclk = ~sysclk; //duty cycle 50%, period 20 ns; Frequency 50Mhz;

endmodule

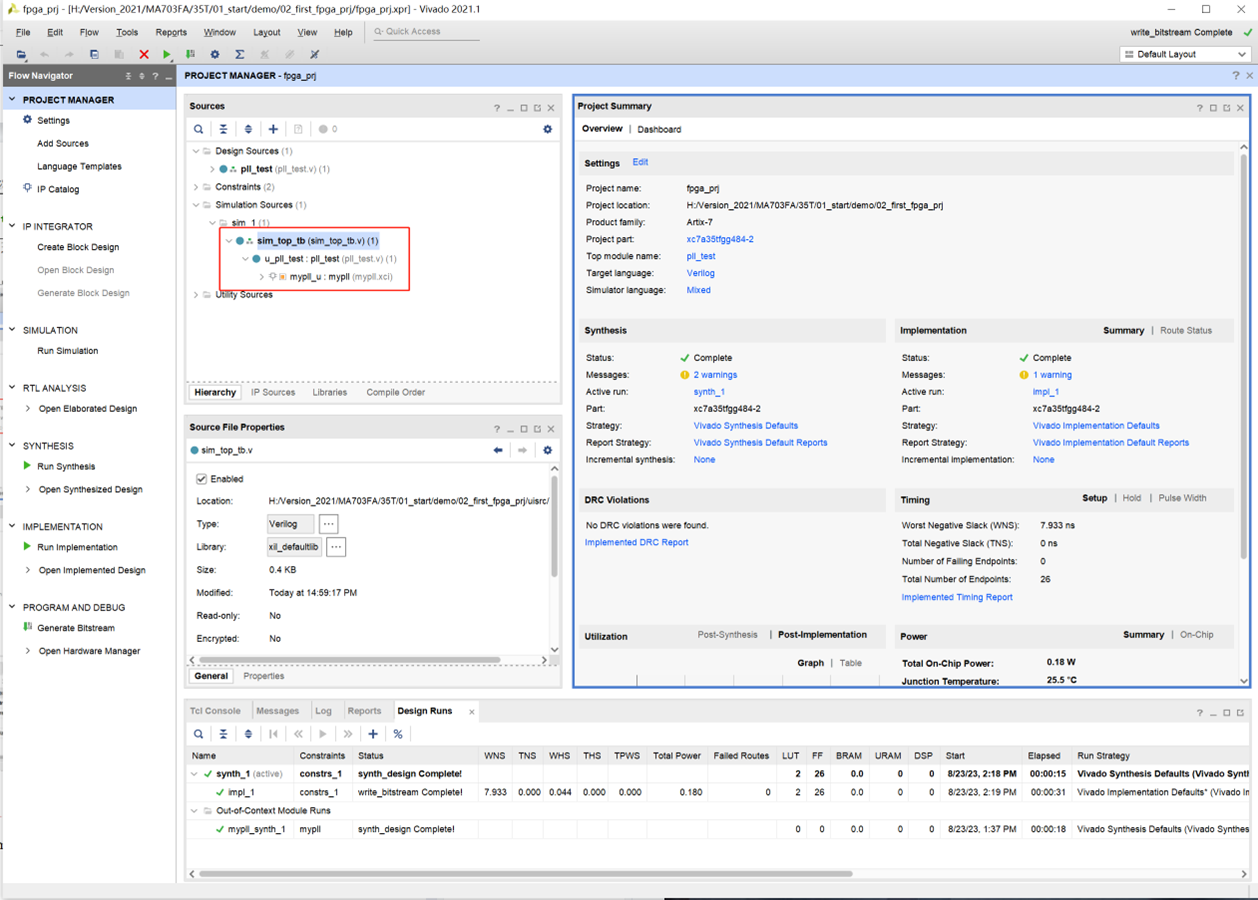

TB文件保存后,我们可以发现,文件结构又发生了变化,主程序并入了我们TB文件下,说明我们程序例化成功,可以开始仿真。

2.3运行仿真

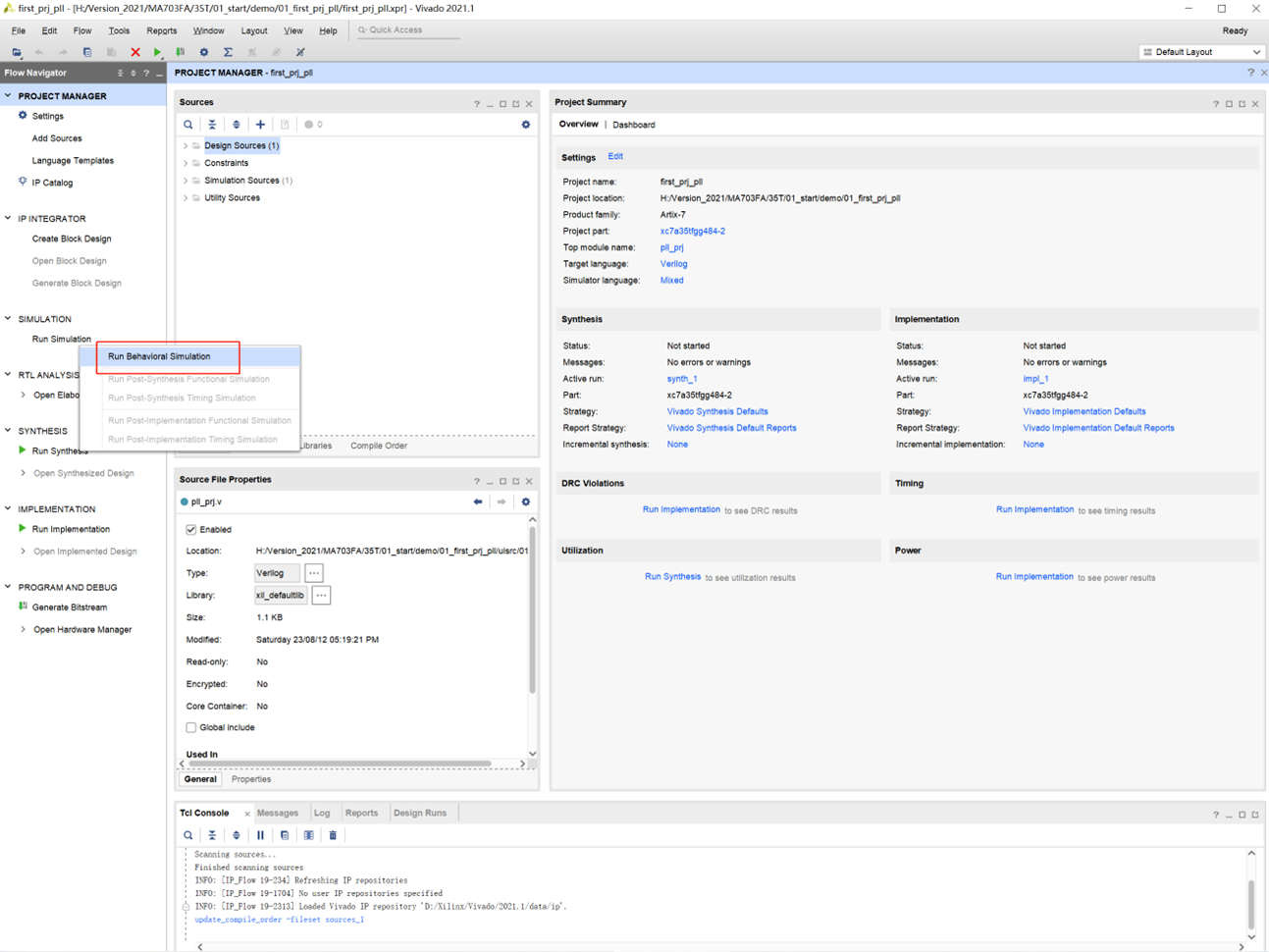

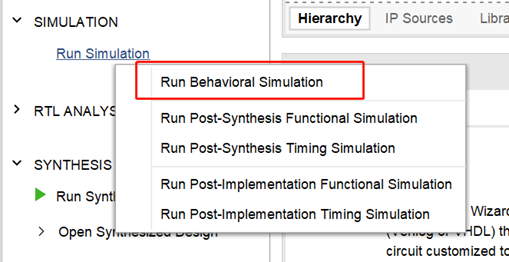

Step1:点击Run Behavioral Simulation

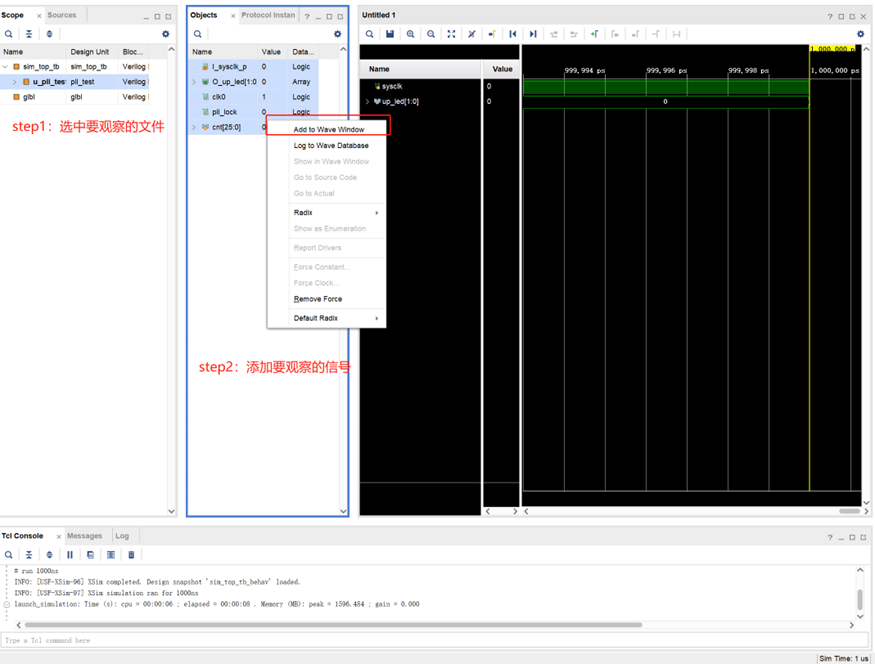

Step2:等待数秒,我们进入仿真界面,这时候我们需要选出我们需要观察的信号,然后右键添加进我们的观察窗口,

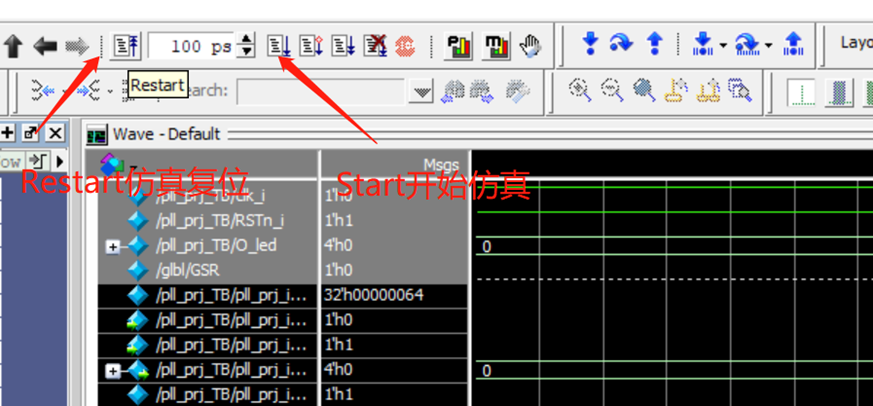

Step3:添加完成后,我们需要重新开始仿真或者刷新一下我们的观察数据,然后点击run运行仿真。

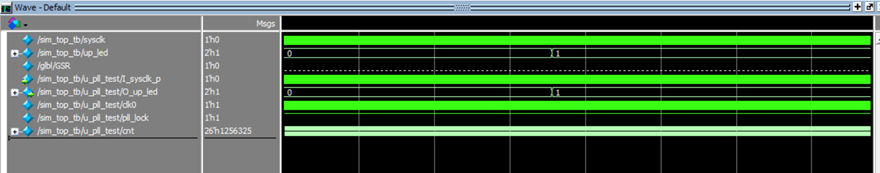

Step4:运行后,由于我们计数器要经过一段时间比较长的计数,所以我们需要等待一段时间。通过结果可以看到经过PLL IP分频出来的时钟跟预期保持一致,LED正常翻转。

3使用Modelsim进行仿真

默认电脑上已经安装完成vivado以及Modelsim软件。

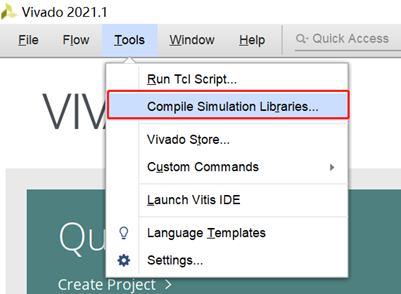

Step1:打开vivado,点击Tools --> Compile Simulation Libraries,生成库函数

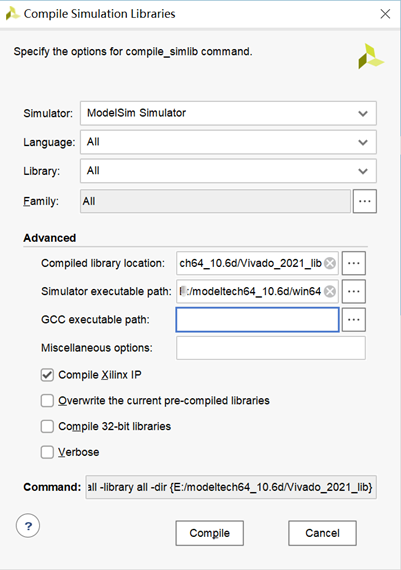

Step2:生成库函数设置

Simulator选择ModelSim Simulator

Language,Library,Family选择全部(All)

Compiled library location:编译库目录,可以选择在ModelSim的安装路径下,新建一个Vivado_2021_lib的文件夹

Simulator executable path:选择ModelSim的启动路径

点击Compile,即可开始生成库文件,等待编译完毕。

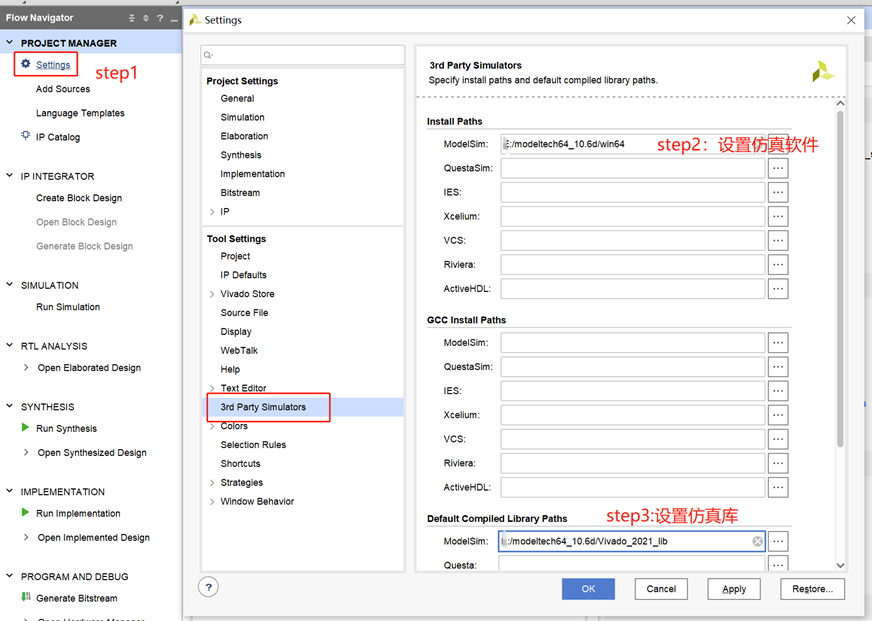

Step3:在Vivado中添加ModelSim调用设置

Vivado --> Tools --> setting,分别设置仿真软件和仿真库

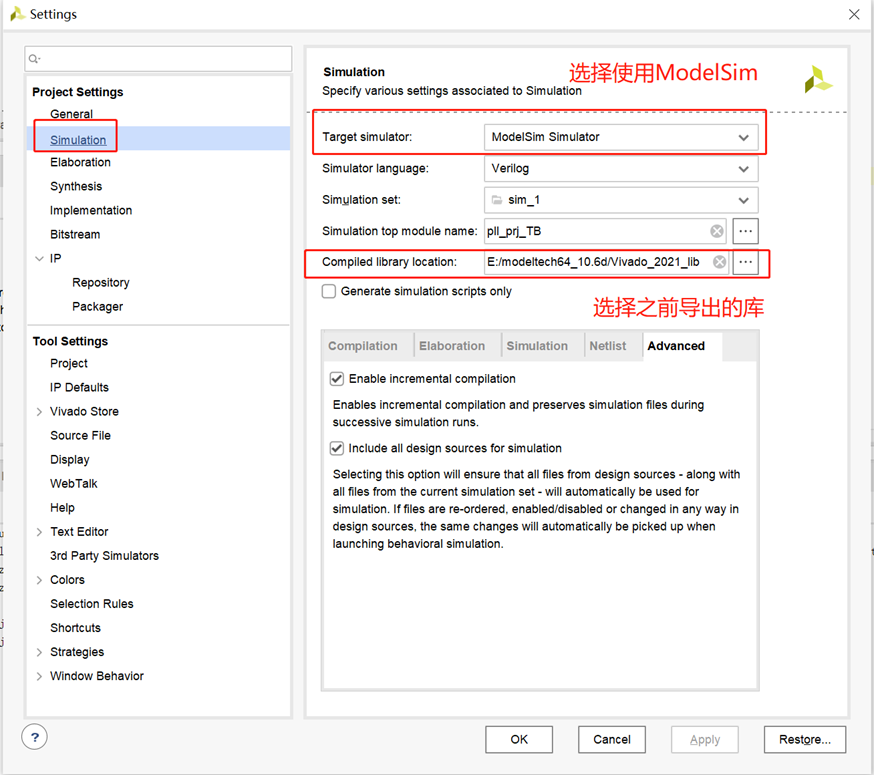

Step4:在Simulation中选择ModelSim来仿真并且调用之前到处的库。

Step5:点击Run Behavioral Simulation,Modelsim正常启动

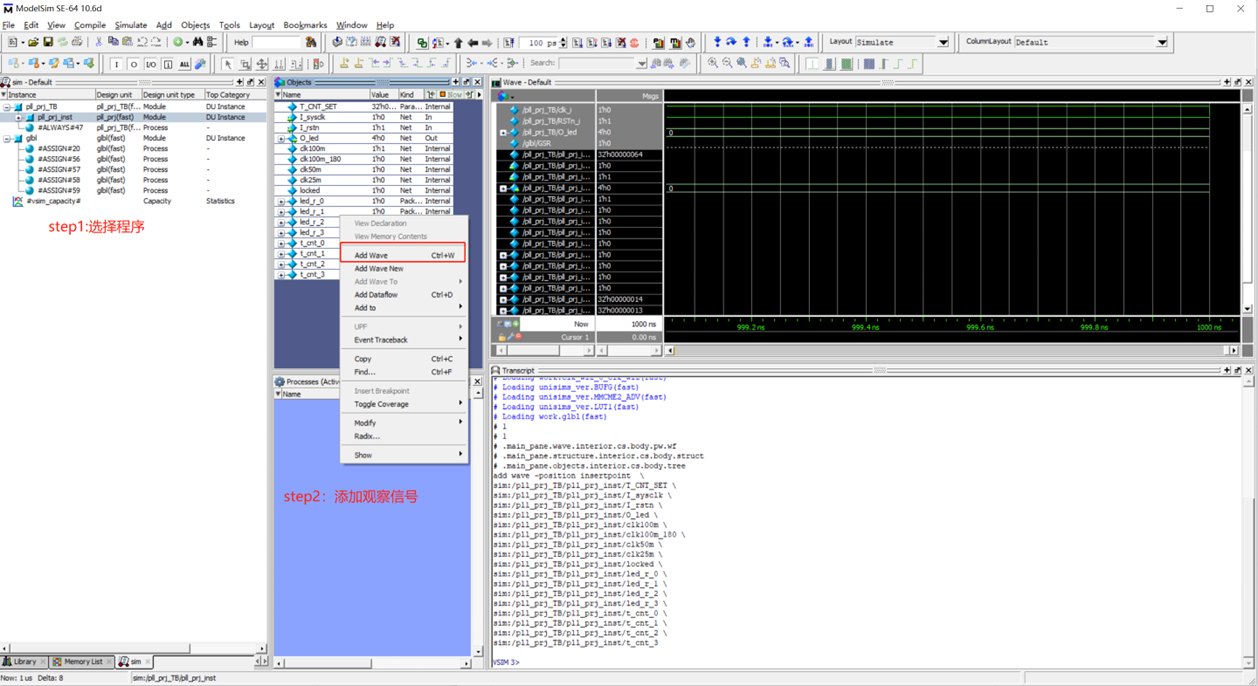

Step5:右键添加信号

Step6:先把信号复位,然后重新开始仿真

Step6:仿真结果无误

4本章小结

本章节主要学习了两种仿真方法,并且分别对工程进行仿真。