文章来源:FPGA的现今未

说到DDR3的接口设计,有一个无法避开的问题,就是DDR3的读写性能,一方面需要一个好的设计来提升DDR3的读写性能,另一方面也需要一个好的测试程序来衡量性能指标。

物理带宽

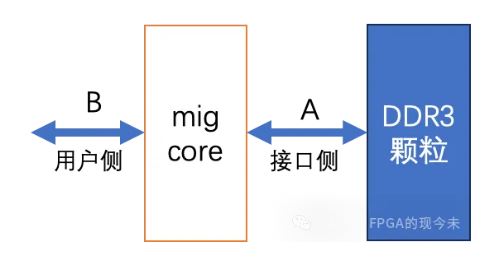

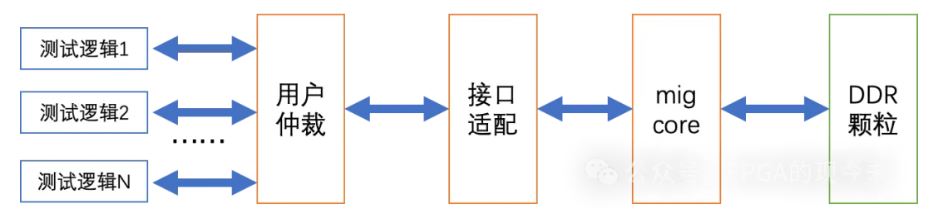

在谈及DDR3的性能的时候,首先要考虑的就是DDR3的物理带宽。假定我们采用的是x16bit的颗粒,4个颗粒拼位宽组成64bit的数据位宽。DDR3的物理带宽可以从2个点去计算,如下图所示,是在FPGA中用户通过mig core和DDR3颗粒连接。可以从接口A和接口B这2个点来计算物理带宽:

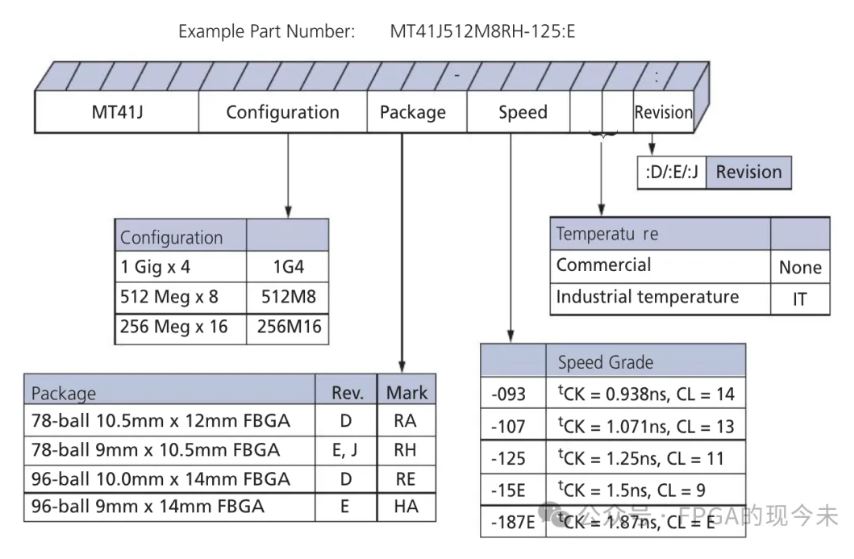

接口A:数据位宽为64bit,时钟频率呢?需要从DDR3颗粒的手册中去寻找,以下图为例子,speed为125,即DDR3支持的最大的IO接口时钟频率为1000/1.25 = 800M,由于DDR3是双沿采样,因此每条数据线的传输速率为1600Mb/s,所以物理带宽就是64bit *1600Mbit/s = 102.4Gbit/s = 12.8GB/s.

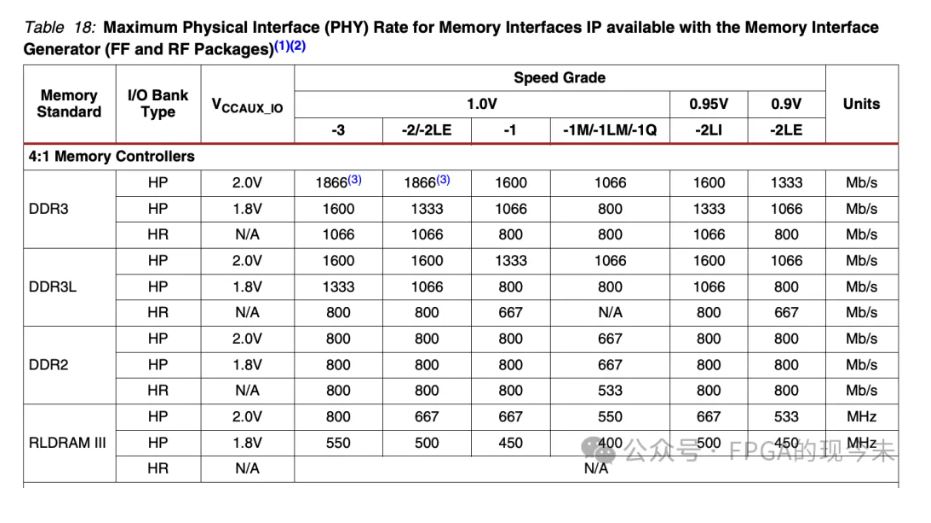

接口A的工作频率,除了和DDR颗粒有关,还和FPGA的IO有关,不同的器件这个速率也是不一样的。如下图所示,K7系列(DS182),FF和RF封装的芯片在不同电压和芯片等级下,不同bank所支持的PHY的最大速率。

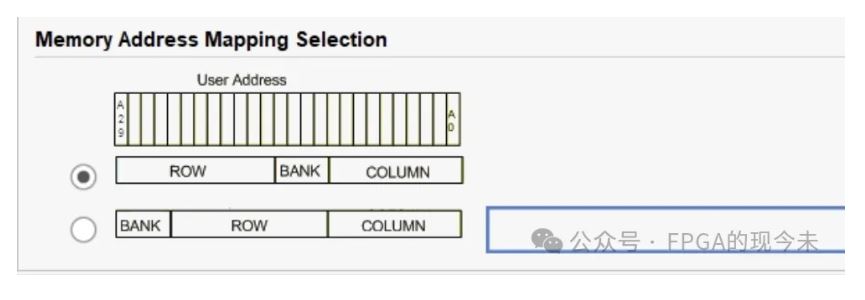

接口B:在例化mig core的时候(具体参考这里:IP的生成),有一个PHY to Controller Clock Ratio的选择,即接口A和接口B的时钟比率,这里选择了4:1,即接口B的时钟频率为200M,通过例化mig core,我们可以看到接口B数据位宽为512bit,因此接口B的性能为 200M*512bit = 102.4Gb/s。即接口A和接口B的位宽是一致的。我们知道DDR3的burst长度为8,即一次操作8个地址,每个地址的数据位宽为16bit(16bit的DDR3颗粒),有4个颗粒,即每个地址的数据位宽为64bit,所以一次burst操作的数据量为64*8=512bit。这也解释了为什么mig core接口B的数据位宽为512bit。

读写性能

对于DDR3的读写操作来说,如何提高性能,是一个永无止境,无限追求物理带宽的过程。对于大多数应用来说,追求这个永无止境的过程是没有意义的。只要满足我们的项目需求即可,或者说以最小的代价,换取最大的性能。这里说明几种最常见的设计方案。

最大的利用行

cache方式

对于在DDR中存放表项的场景,经常要“随机”的访问DDR,且每次读写的长度都比较小,比如128byte,在这种场景下,要么牺牲一定的带宽来满足性能,要么就减少对表项的访问次数(一般也是采用这个方案),这个可以在外部增加一个“cache”来实现。具体可以参考FPGA中如何设计一个小cache(一)、FPGA中如何设计一个小cache(二)。

读写性能测试逻辑

DDR性能的测试,主要是不同突发长度和不同地址模式的组合测试。不同突发长度比较好理解,就是用户一次读写操作的长度。一般是从32byte、64byte、128byte……一直到4096byte或者8192byte。地址模式主要是看访问DDR的地址是顺序地址还是随机地址。因此就可以得到不同的组合,从而可以比较全面地反映出性能情况。

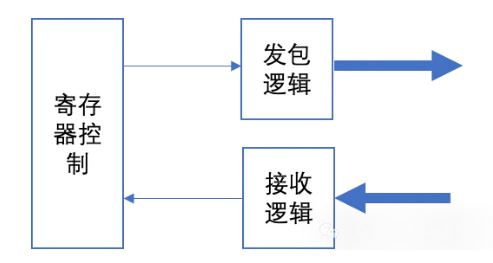

测试逻辑的设计的框图如下图所示:

核心模块就2个,发包逻辑和接收逻辑。发包逻辑支持发送不同长度的写数据和写命令,支持发送不同长度的读命令。对于地址要支持顺序地址和随机地址,同时也要支持添加校验位。接收逻辑主要是对收到的数据进行校验,判断读出的数据是否正确。

总结

DDR的性能,根据参数是可以理论计算的。但是实际情况可能会有一定的出入,尤其是针对不同的场景,读写操作的模式都是不一样的,另外不同的厂家所设计的mig core的效率也不相同,因此对DDR需求比较严格的场景下,一个比较好的评估方案就是实际测试,提前确认好对DDR性能的需求和实际的设计能力。