文章来源:AMD开发者社区

几乎所有 AMD 可编程器件都具有 CLB 资源,可以在 LUT 中实现小型存储器。

在网表中,这些资源被称为 LUTRAM 或分布式 RAM。这些 LUTRAM 不像 Vivado 中的其他单元那样遵循典型结构。本文说明了推断或例化的 LUTRAM 的结构。

在相应架构的《库指南》中列出了可用的各种类型的 LUTRAM 原语。以下提供了一些参考资料。

Versal Premium - https://docs.amd.com/r/en-US/ug1485-versal-architecture-premium-series-libraries/RAM128X1D

Versal Prime - https://docs.amd.com/r/en-US/ug1344-versal-architecture-libraries/RAM128X1D

UltraScale+ 及更低版本 - https://docs.amd.com/r/en-US/ug974-vivado-ultrascale-libraries/RAM128X1D

Vivado 中的网表包含端口、信号线、单元(层级和叶级)。

叶节点单元是将布局在器件物理位置的最低单位级单元。层级单元是一个封装文件,它是叶节点单元的集合。典型的网表由层级单元与叶节点单元混合组成。

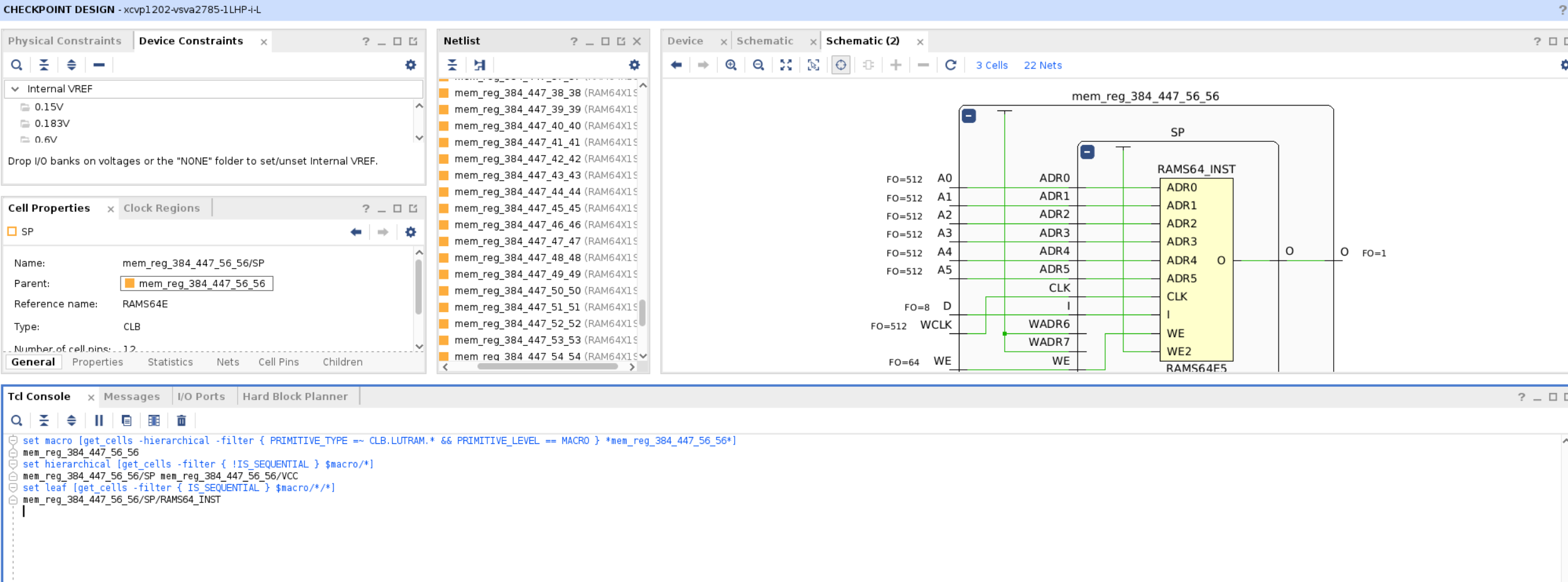

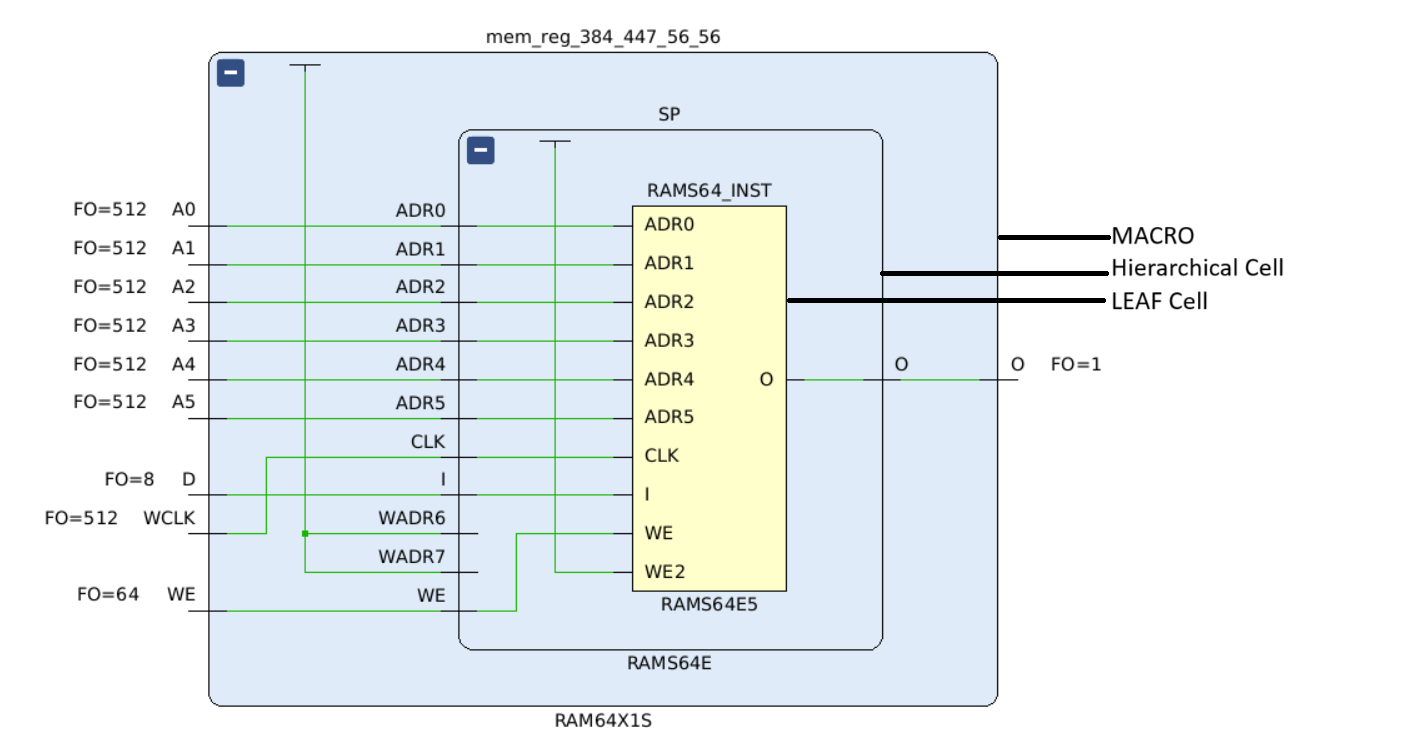

下图显示了 Versal 器件的 LUTRAM 原语:

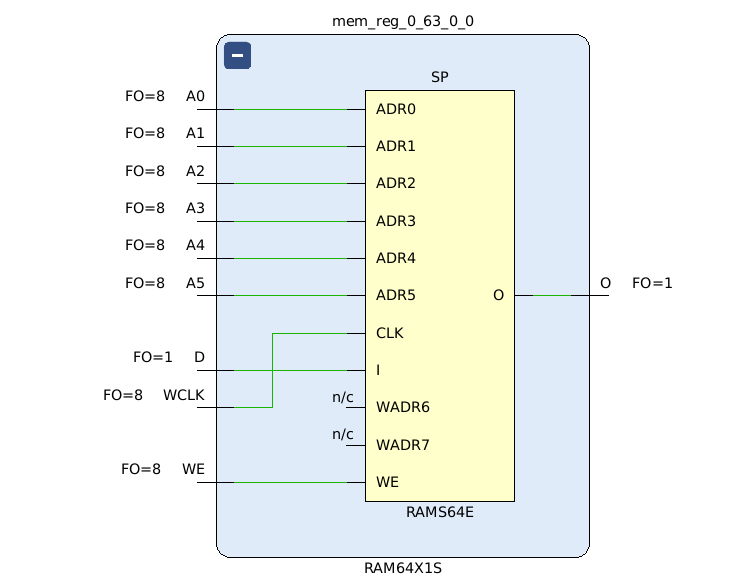

下图显示了 7 系列和 UltraScale 器件的 LUTRAM 原语:

Vivado 中的 LUTRAM 与典型网表的不同之处如下所述:

它由 Versal 器件的 3 个单元组成:

宏单元

层级单元

叶节点单元

对于 UltraScale+ 和 7 系列,它由 2 个单元组成

宏单元

叶节点单元

宏单元是将由综合工具推断或由用户例化的原语。LUTRAM 宏单元内有一个层级单元,该层级单元包含一个叶节点单元,它是 LUTRAM 的单位级元素。

LUTRAM 以上述方式建模,因为 Vivado 必须支持器件上的多种存储器配置使用相同 CLB 资源。

注:如上图所示,对于 7 系列和 UltraScale+ 器件中的 LUTRAM 原语,不存在层级单元。

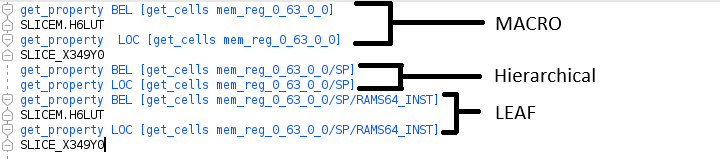

当我们查询这些不同单元的 BEL 和 LOC 属性时,该工具仅返回宏单元和叶节点单元的这类属性。

在宏级别,即使以下原语单元分布在多个 SLICE 上,也会返回单一值。

这是默认行为,不应该作为查询 LUTRAM 的首选方式。建议的方式即对叶节点单元运行“get_properties”,如上例所示。

要返回宏,请使用以下命令:

set macro [get_cells -hierarchical -filter { PRIMITIVE_TYPE =~ CLB.LUTRAM.* && PRIMITIVE_LEVEL == MACRO } *mem_reg_384_447_56_56*]

mem_reg_384_447_56_56要返回层级单元,请使用以下命令:

set hierarchical [get_cells -filter { !IS_SEQUENTIAL } $macro/*]

mem_reg_384_447_56_56/SP mem_reg_384_447_56_56/VCC要返回叶节点单元,请使用以下命令:

set leaf [get_cells -filter { IS_SEQUENTIAL } $macro/*/*]

mem_reg_384_447_56_56/SP/RAMS64_INST