AI Engine Tile 架构

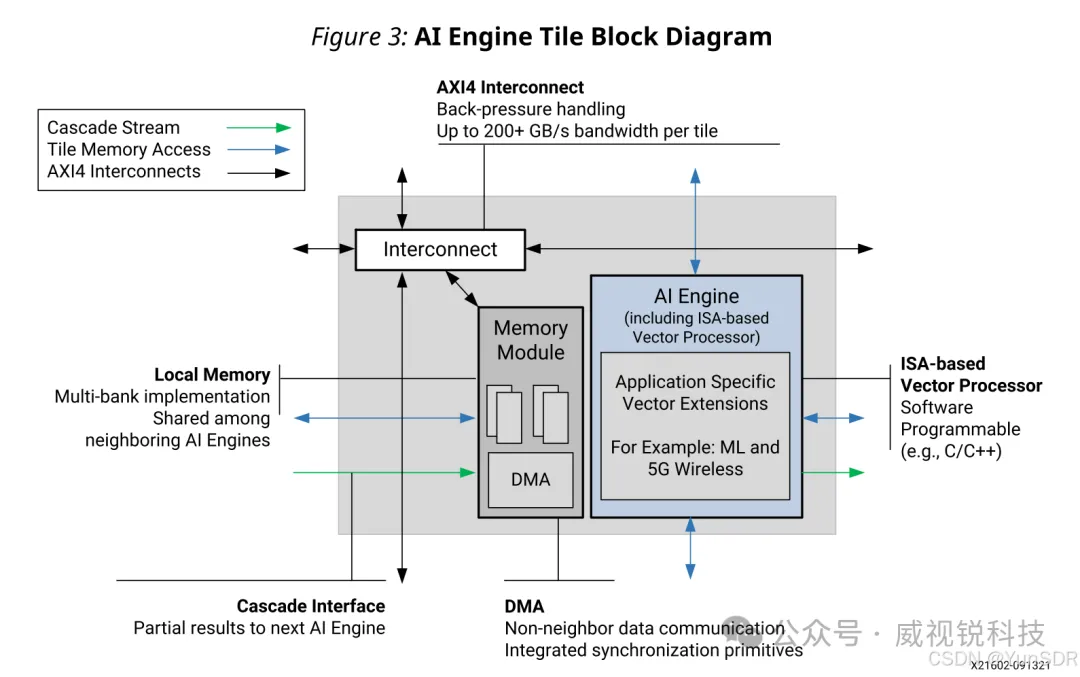

AI Engine Tile架构的顶级框图、关键构建模块和AI Engine Tile的连接如下图所示:

•AI Engine Tile由以下高级模块组成:

•tile互连

•AI Engine

•AI Engine内存模块

tile互连模块会处理AXI4流和内存映射的AXI4输入/输出流量。存储器映射的AXI4和AXI4流互连将在以下部分中进一步描述。AI Engine内存模块有32 KB的数据内存,分为八个存储体、一个内存接口、DMA和锁。传入和传出方向都有DMA,每个内存模块内都有一个Locks块。AI Engine可以将所有四个方向的内存模块作为一个连续的内存块进行访问。内存接口根据AI Engine生成的地址将内存访问映射到正确的方向。AI Engine有一个标量处理器、一个向量处理器、三个地址生成器和16KB的程序内存。它还具有级联流访问,用于将累加器输出转发到下一个AI Engine Tile。AI Engine在第4章:AI Engine架构中有更详细的描述。AI Engine和AI Engine内存模块都有控制、调试和跟踪单元。本章稍后将介绍其中一些单元:

•控制和状态寄存器

•事件、事件广播和事件操作

•用于分析和计时器的性能计数器

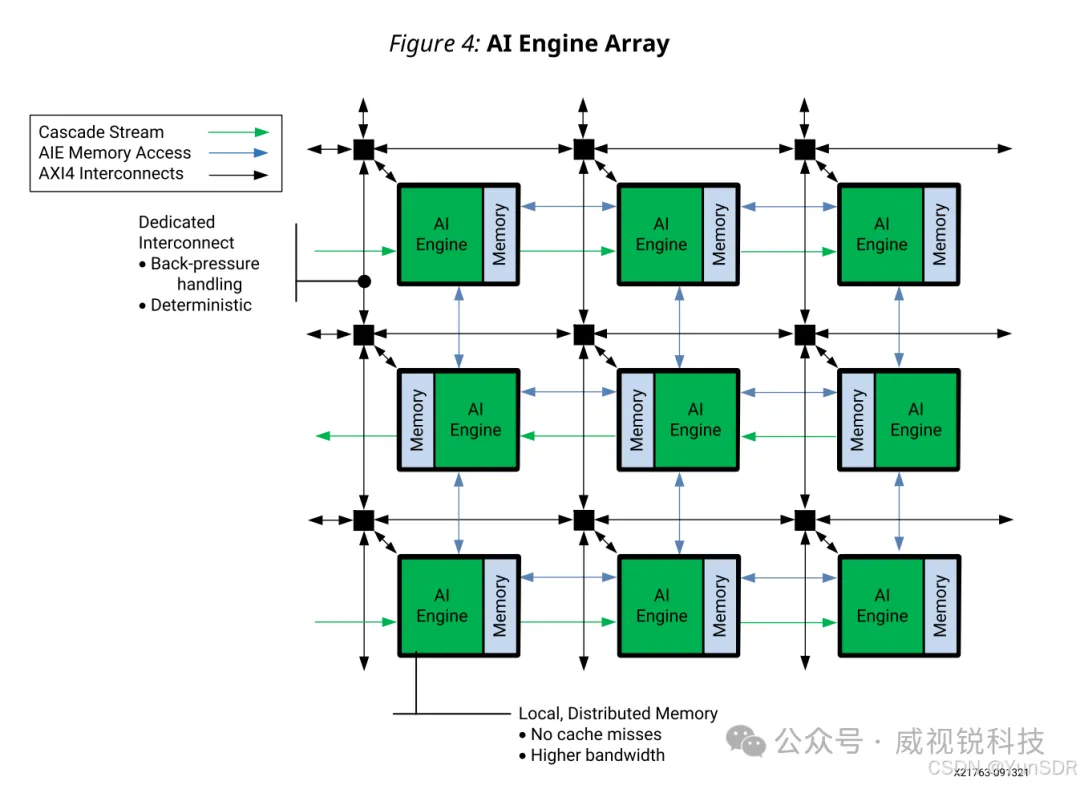

下图显示了AI Engine阵列,其中AI Engine Tile和专用互连单元排列在一起。在相邻的AI Engine之间与本地内存共享数据是AI Engine阵列内数据移动的主要机制。每个AI Engine最多可以访问四个内存模块:

•它自己的 •北部的模块 •南部的模块 •东部或西部的模块,具体取决于AI Engine和内存模块的行和相对位置。 阵列边缘的AI Engine可以按照棋盘模式访问一个或者两个更少的内存模块。

结合灵活和专用的互连,AI Engine阵列提供了确定性的性能、低延迟和高带宽。模块化和标量架构允许更多的计算能力,因为阵列中添加了更多的tile。级联流以水平方式从底层流到顶层。当级联流到达一端的边缘时,它会连接到其上方tile的输入端。因此,流在交替的行上改变方向(一行从西向东,另一行从东向西)。级联一直持续到到达最上面一行的一端,此时流结束,没有进一步的连接。由于方向的改变,AI Engine和内存模块在tile中的相对位置从一行颠倒到另一行。

内存映射AXI4互连

每个AI Engine Tile都包含一个内存映射的AXI4互连,供外部块用于向AI Engine Tile中的任何寄存器或内存写入或读取。AI Engine阵列内的内存映射AXI4互连可以由任何可以连接到片上网络(NoC)的AXI4主机从AI Engine阵列外部驱动。AI Engine Tile中的所有内部资源,包括内存,以及AI Engine和AI Engine内存模块中的所有寄存器,都映射到内存映射的AXI4接口上。

每个AI Engine Tile都有一个内存映射的AXI4开关,该开关将接受来自南方向的所有内存映射AXI4访问。如果地址是用于互动程序的,则会发生访问。否则,访问权限将传递到北方向的下一个tile。

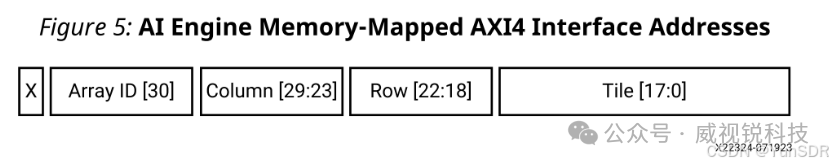

下图显示了AI Engine Tile中内存映射AXI4的寻址方案。较低的18位表示0x0000到0x3FFFF的块地址范围,后面是表示行位置的5位和表示列位置的7位。

AI Engine内部内存映射的AXI4互连是全内存映射AXI4协议的一个子集,具有以下限制:

•写地址前没有写数据 •写数据只有一个WSTRB信号 •只有一到四个32位字的突发 •32位固定大小

AXI4流互连

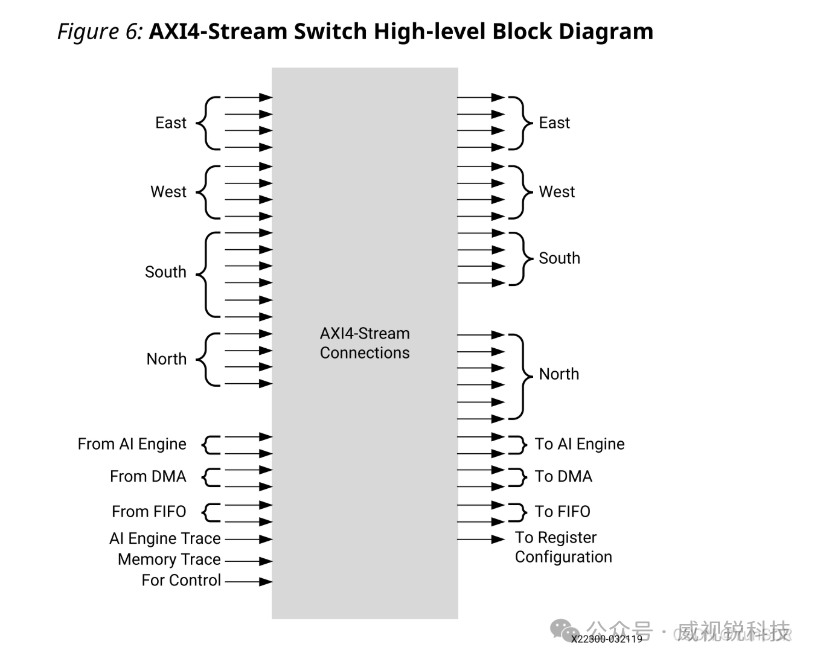

每个AI Engine Tile都有一个AXI4流互连(也称为流交换机),它是一个完全可编程的32位AXI4串交叉开关,并通过内存映射的AXI4互连进行静态配置。它可以处理背压,并能够在AXI4流上实现全带宽。下图是AXI4流交换机的高级框图。交换机有主端口(从交换机流出的数据)和从端口(流向交换机的数据)。下图显示了AXI4流互连。AXI4 Stream互连的构建块如下端口处理程序。

•端口处理器 •FIFO •仲裁器 •流交换机配置寄存器 每个端口都有一个端口处理程序,用于选择输入/输出流的路由。每个主端口和从端口都包含一个4深度FIFO的缓冲区,具有两个周期的延迟。每个流交换机都有两个FIFO缓冲区(16深,32位数据+1位TLAST宽),可以链接在一起,用于向流中添加缓冲。每个交换机都有六个用于分组交换的可编程仲裁器。

每个流端口都可以使用配置寄存器中的分组交换位配置为电路交换或分组交换流(永远不会同时)。电路交换流是一对多流。这意味着它只有一个源端口和任意数量的目标端口。在源处进入流的所有数据都会流式传输到所有目的地。分组交换流可以与其他逻辑流共享端口(从而共享物理线路)。由于存在与其他分组交换流发生资源争用的可能性,因此它们不提供确定性延迟。电路交换流中传输的字的延迟是确定的;如果带宽有限,内置背压将导致性能下降。

分组交换流由5位ID标识,该ID在与之共享端口的所有流中必须是唯一的。流ID还标识了数据包的目的地。目的地可以是任意数量的主端口,分组交换流可以实现任何给定流中单个/多个主/从端口的所有组合。

包交换包具有:

•包头:包的路由和控制信息

•数据:包中的实际数据

•TLAST:包中最后一个字必须声明TLAST以标记包的结束。

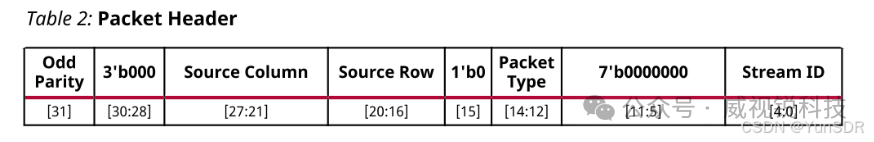

包头显示如下:

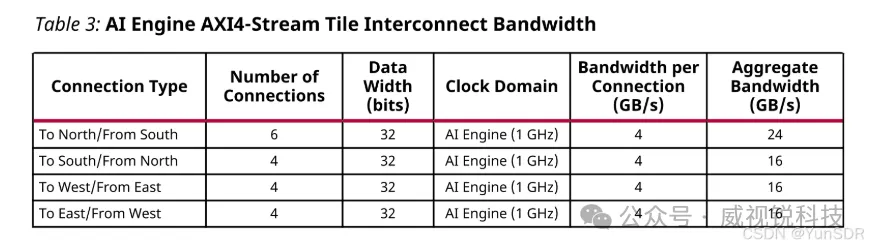

下表总结了-1L速度级设备的AXI4流块互连带宽。

AI Engine Tile程序内存

AI Engine有一个16KB的本地程序内存,可用于存储VLIW指令。程序内存有两个接口:

•内存映射AXI4接口

•AI Engine接口

外部主机可以使用内存映射AXI4接口读取或写入程序内存。AI Engine具有128位宽的程序存储器接口,用于获取指令。AI Engine可以读取程序内存,但不能写入。要从内存映射的AXI4和AI Engine同时访问程序内存,请将内存划分为多个存储体,并访问程序内存中互斥的部分。需要仲裁逻辑来避免访问之间的冲突,并在访问同一bank时分配优先级。如果来自内存映射AXI4和AI Engine的访问都是对同一存储体的,则AI Engine具有更高的优先级,内存映射AXX4访问返回从属错误。

AI Engine接口

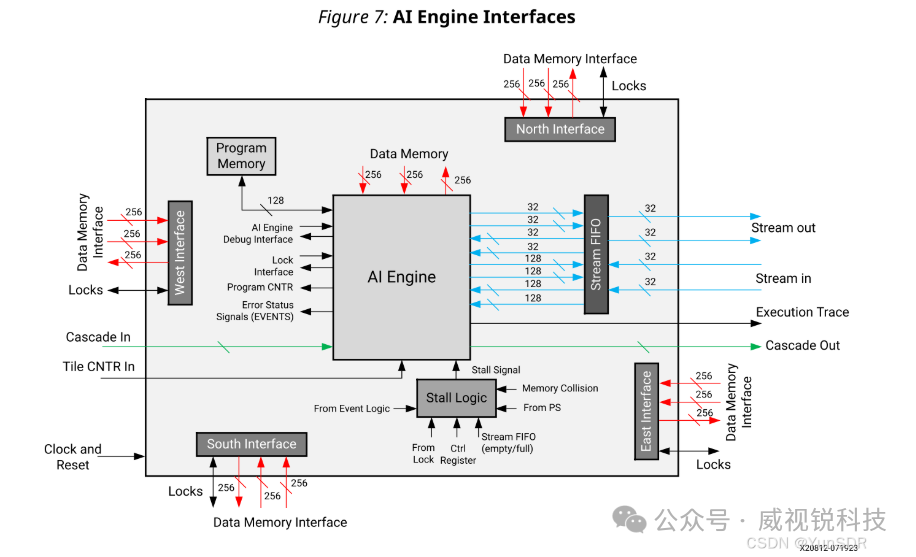

AI Engine有多个接口。以下框图显示了接口。

•数据存储接口:AI Engine可以在所有四个方向上访问数据存储模块。它们作为一个连续的内存进行访问。AI Engine有两个256位宽的加载单元和一个256位宽存储单元。从AI Engine的角度来看,每个负载(两个)和存储(一个)的吞吐量为每个时钟周期256位程序内存接口:这个128位宽的接口由AI Engine用来访问程序内存。每个时钟周期都可以获取一条新指令。

•直接AXI4流接口:AI Engine有两个32位输入AXI4串流接口和两个32位元输出AXI4 Stream接口。每个流在输入和输出侧都连接到FIFO,允许AI Engine每4个周期进行4个字(128位)的访问,或者在流上每周期进行1个字(32位)的存取。

•级联流接口:通过使用这些级联流形成链,可以将来自一个AI Engine的384位累加器数据转发给另一个。输入和输出流上都有一个小的、两层深的、384位宽的FIFO,允许在AI Engine之间存储多达四个值。

•调试接口:该接口能够通过内存映射的AXI4接口读取或写入所有AI Engine寄存器

•硬件同步(锁定)接口:此接口允许两个AI Engine之间或AI Engine和DMA之间的同步。AI Engine可以从四个方向访问。

•锁处理:AI Engine可能会因多种原因和不同来源而被锁住。示例包括:外部内存映射的AXI4主机(例如PS)、锁模块、空或满AXI4流接口、数据内存冲突以及来自事件单元的事件操作。

•AI Engine事件接口:这个16位宽的Event接口可用于设置不同的事件。

•Tile定时器:读取Tile内64位定时器值的输入接口。

•执行跟踪接口:一个32位宽的接口,AI Engine生成的基于包的执行跟踪可以通过AXI4流发送。

AI Engine内存模块

AI Engine内存模块(如下图所示)包含八个存储体、两个输入流到内存映射(S2MM)DMA、两个内存映射到输出DMA流(MM2S)和一个硬件同步模块(锁)。对于四个方向(南、西、北和东)中的每一个,偶数和奇数端口都有单独的端口,以及三个地址生成器、两个负载和一个存储。

•内存组:AI Engine内存模块由八个内存组组成,每个内存组是一个256字x 128位的单端口内存。每个存储体对每个32位字都有一个写启用。存储体[0-1]具有ECC保护,存储体[2-7]具有奇偶校验。存储体[0]从内存模块的地址0开始。ECC保护是每32位字1位错误检测器/校正器和2位错误检测器。

•内存仲裁:每个内存库都有自己的仲裁器,在所有请求者之间进行仲裁。内存库仲裁是循环的,以避免饿死任何请求者。它在每个时钟周期处理一个新请求。当同一周期内对同一存储体有多个请求时,每个周期只允许一个请求访问内存。其他请求程序将暂停一个周期,硬件将在下一个周期重试内存请求。

•Tile DMA控制器:tile DMA有两个传入和两个传出流到AI Engine Tile中的流交换机。块DMA控制器分为两个单独的模块,S2MM用于将流数据存储到内存(32位数据),MM2S用于将内存的内容写入流(32位数字)。每个DMA传输由DMA缓冲描述符定义,DMA控制器可以访问16个缓冲描述符。这些缓冲区描述符也可以使用内存映射的AXI4互连进行配置。每个缓冲区描述符包含DMA传输所需的所有信息,并且可以指向下一个DMA传输,以便DMA控制器在当前DMA传输完成后继续进行。DMA控制器还可以访问16个锁,这是AI Engine和DMA或任何外部存储器映射的AXI4主机(AI Engine阵列之外)和DMA之间使用的同步机制。每个缓冲区描述符都可以与锁相关联。这是使用内存映射AXI4互连配置任何缓冲区描述符的一部分.

•锁定模块:AI Engine内存模块包含一个锁定模块,用于实现AI Engine、块DMA和外部内存映射的AXI4接口主控器(例如处理器系统(PS))之间的同步。每个AI Engine内存模块锁单元有16个具有二进制数据值的硬件锁。每个锁都有一个仲裁器,用于同时进行请求管理。锁模块处理来自所有四个方向的AI Engine、本地DMA控制器和内存映射AXI4的锁请求。

文章来源:威视锐科技