1. 引言

在现代异构计算架构中,FPGA的可编程逻辑阵列以其高度灵活性著称。但仅靠查找表(LUT)和触发器构成的标准逻辑单元处理复杂算法时,往往面临资源开销大、时序收敛难、功耗攀升等现实瓶颈。DSP硬核资源的嵌入,恰为这一困境提供了优雅的解决方案——它将专用乘法器、累加器及流水线寄存器以硬化形式集成于可编程 fabric 之中,与周边可编程逻辑形成"刚性算力+柔性互联"的互补格局。这种架构设计使得FPGA能够高效的支撑起高吞吐量的并行信号处理任务,真正释放了FPGA器件在高性能计算领域的核心价值。

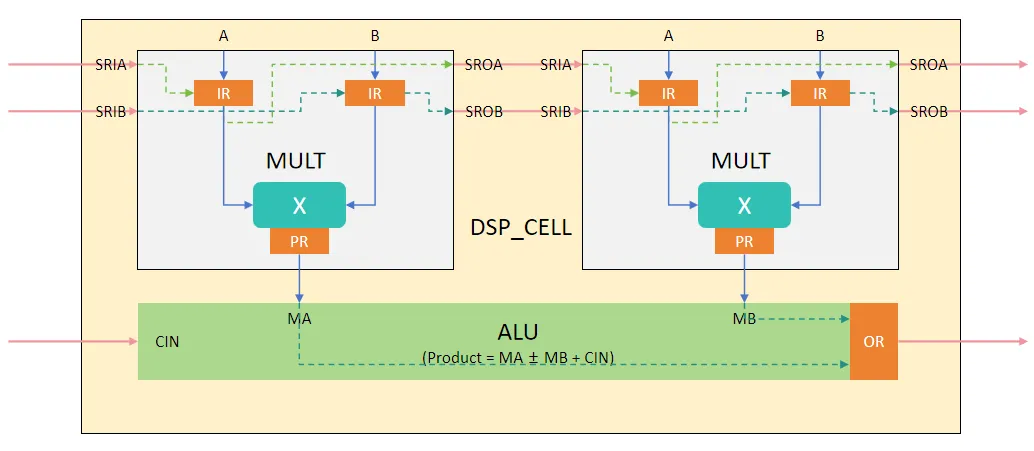

2. 智多晶DSP硬件架构

智多晶的一个典型的DSP单元包含2个乘法器(MULT18),1个算数逻辑单元(ALU)。其中DSP上的输入级寄存器可进行垂直方向上的输入寄存或横向的移位寄存,另在每一个运算单元(乘法器,ALU)都支持运算模式和输出寄存等配置,以硬件优化的方式实现典型和特异型的DSP运算。

3. IP应用简介

由于DSP是硬件,其应用具有极高的复杂度,与器件的特异性关系密切,用户很难全面的理解和直接使用DSP硬件。除FIR,FFT等特定算法应用IP外,智多晶对DSP的通用型应用提供了两个IP,通过图形化界面简化理解,实现复杂的底层配置,方便用户调用。

DSP_Calculator IP:

主要针对单个DSP单元支持的最多5种(依器件而定)运算表达式的配置,且开放ALU模块的X端通路路径的配置,实现多级级联或单级循环运算的支持。

IP特性:

支持5种运算表达式

R=A0±B0±X R=A0*B0±X R=A0*B0±A1*B1±X R=(PA0+PA1)*B0±X R=(PA0+PA1)*B0±(PA2+PA3)*B1±X) 具备可配置源的可变 X 通道 加减法运算符控制 支持用户自定义输入数据格式(位宽、类型) 支持用户自定义寄存器拍数(0~3) 生成的 IP 支持 DSP 级联和自反馈应用

Hyper_DSP IP:

主要针对通过DSP单元级联可实现的超大位宽DSP应用提供支持。

IP特性:

支持乘法和乘加/减两种运算表达式 乘法器支持最高 72×72 输入 支持用户自定义输入数据格式(位宽、类型) 支持最多 4 种时序性能优化选项 可配置同步/异步复位模式

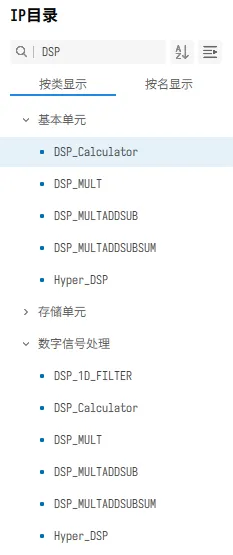

4. IP的调用和用户手册

在HqFpga软件中,首先确保当前工程已处于激活状态,随后点击界面顶部的"IP管理"按钮,即可唤出IP管理器。该管理器会自动识别工程中所选器件型号,并据此筛选出兼容的IP列表。本文涉及的两个DSP IP位于"基本单元"和"数字信号处理"分类下,也可直接在搜索框中输入"DSP"快速定位。双击目标IP名称,即可进入参数化配置界面。

智多晶HqFpga软件为每个IP均配有详尽的用户文档——点击IP配置界面中的"用户手册"按钮即可直接调阅当前IP的用户手册。建议免费下载安装HqFpga软件,亲身体验这两款DSP IP的实际效果;更多配置细节与使用技巧,可参考IP用户界面和用户手册获取详细应用指导。

如有更多问题请联系智多晶销售或技术支持。

文章来源:智多晶