经过BUFGMUX的时钟该如何约束

judy 在 周二, 12/12/2023 - 09:27 提交

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑

本文介绍一种通过SystemC做RTL/C/C++联合仿真的方法

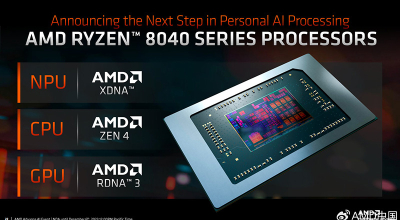

AMD宣布推出全新的锐龙8040系列移动处理器,凭借一流的x86处理器性能,扩展了其在移动产品领域的领先地位

今天介绍一下Cordic算法和Xilinx的Cordic IP。

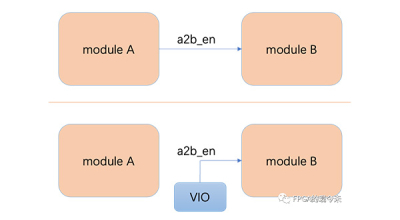

在以往的项目中,要控制FPGA内部某个信号的值,往往是通过配置寄存器来实现的

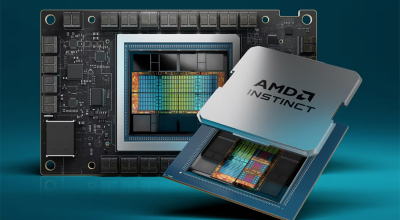

AMD 使用最先进生产技术打造了 MI300 系列,并采用“3.5D”封装等新技术来生产两款芯片

本指南提供 AMD Versal™ 自适应 SoC 硬件功能以及创建或移植设计时的块级注意事项的概述

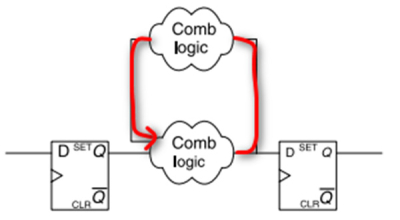

组合逻辑环路:指组合逻辑的输出信号不经过任何时序逻辑电路(FF等)

MI300X 计算单元增加近 40% 、内存容量增加 1.5 倍、峰值理论内存带宽增加 1.7 倍

本文介绍一种方法在petalinux环境下使用OpenCV的Python API实现USB camera视频流的读取显示。