如何在Vivado中用工程模式使用DFX流程

judy 在 周二, 04/23/2024 - 15:33 提交

本文介绍在Vivado中用工程模式使用DFX流程以及需要注意的地方。

本文介绍在Vivado中用工程模式使用DFX流程以及需要注意的地方。

AMD 表示,它有望在 5 月底发布其微引擎调度程序 (MES) 文档,随后发布源代码。然后,它将继续以开源方式发布 Radeon 堆栈的其他部分

在工作中,我们接触到的至少90%以上的FPGA项目,它的的资源/时序都有很大的优化空间,为啥这么说?

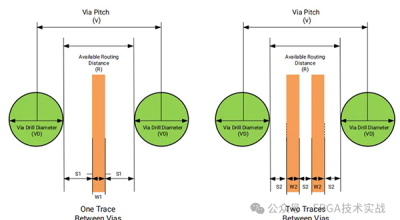

Xilinx®Versal®体系结构、UltraScale™体系结构、7系列和6系列设备有多种封装,旨在实现最大性能和最大灵活性

使用IBERT测试误码率和眼图必须有个收发环通的硬件,开发板上有2个SFP光纤接口,本实验把2个光接口收发两两连接,形成2个收发环通链路。

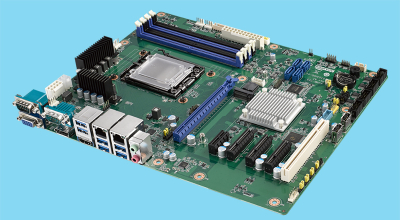

本文将讨论Advantech如何帮助客户利用AOI生产PCB和IC。重点介绍研华的由AMD驱动的AIMB-723工业级主板的新能力

半导体行业正在准备从基于专有小芯片的系统向更加开放的小芯片生态系统迁移

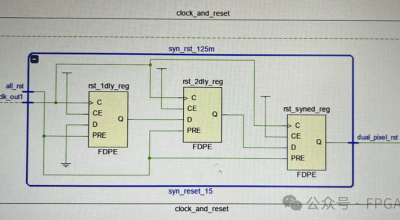

最近一个朋友私信我说,看了以前的写的复位设计,在自己的项目中设计了复位同步器用来实现异步复位同步解复位

DDR完成上电初始化后,将数据写入DDR要经过如下过程:ACT->WR->PRE

RT Box 1中使用的Mercury ZX5采用AMD Xilinx® Zynq® 7015/7030 SoC器件,配备ARM®双核Cortex™-A9处理器