Vitis 库流程 - 在 Zynq 裸机设计中使用视觉库 L1 remap 函数的示例

judy 在 周一, 07/31/2023 - 11:31 提交

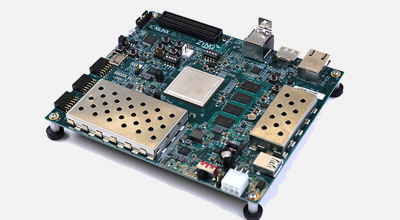

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

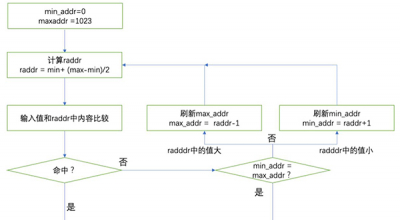

在 PCI Express 诞生 20 周年之际,我们回顾一下这一盛行的扩展插槽的过去和未来

选择创建Block Design并命名,点击Add IP,并选择ZYNQ7

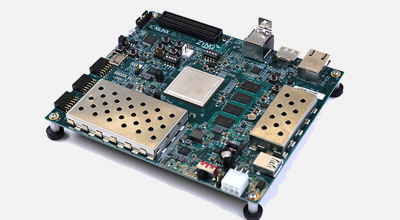

二分法查找算法是在软件中广泛应用的一种算法,那么在FPGA的设计中是否可以用这种算法呢?

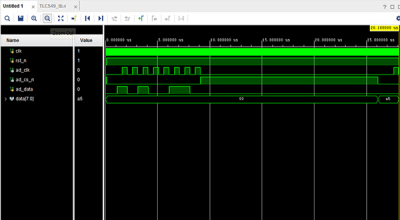

在Vitis流程中,编译的目标分为软件仿真,硬件仿真以及硬件

在生活中,数模转换的例子到处可见。但是在我们做FPGA设计时

ADI官方默认搭配的SD卡种烧写的是与ZC706开发板配套的系统镜像

SmartNIC提供广泛的数据存储和可编程性,但它需要DPU提供更多的虚拟化能力

承接上一篇blog介绍xbmgmt,这次来介绍xbutil的使用方法

本次内容我们看下AXI VIP当作master时如何使用