Xilinx 7系列FPGA 高性能(HP)接口与2.5V/3.3V 外设IO接口设计考虑

judy 在 周二, 05/16/2023 - 10:16 提交

Xilinx 7系列FPGA IO Bank分为HP Bank和HR Bank,HP IO接口电压范围为1.2V~1.8V

Xilinx 7系列FPGA IO Bank分为HP Bank和HR Bank,HP IO接口电压范围为1.2V~1.8V

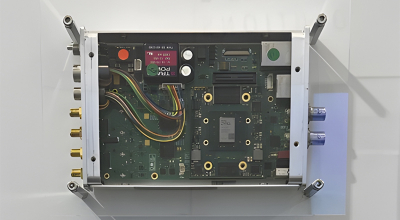

无线电视系统的设计依赖于一些关键的技术和构建模块。FPGA技术可以在无线电视应用中发挥重要作用

在Vitis的 “File - New ” 中,选择“Platform Project”, 指定名称如“zcu106_r5”

如何在 FPGA 中进行简单和复杂的数学运算。

FPGA中的Bank和Clock Region有什么关系?这应该是很多FPGA工程师都很困惑或者没有认真相关的一个问题

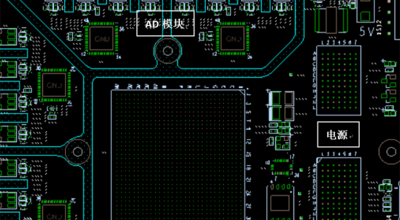

本文给大家分享串行ADC布局布线设计要点!

探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用

有客户需要通过PCie从Windows系统访问MPSoC的DDR,从而使X86和A53通过共享DDR内存的方式交互大量数据

本文重点介绍cache在FPGA中的实现方案

通信服务提供商往往采用无源光网 (PON) 为最终用户带来高速和低成本的光纤接入