ZYNQ 定时器中断实验——FPGA Vitis篇

judy 在 周二, 05/23/2023 - 09:23 提交

本实验介绍如何使用ZYNQ芯片PS端的定时器资源

本实验介绍如何使用ZYNQ芯片PS端的定时器资源

最近在上板测试的过程中,使用mark_debug跑工程后生成的bit在下载的时候遇到了问题

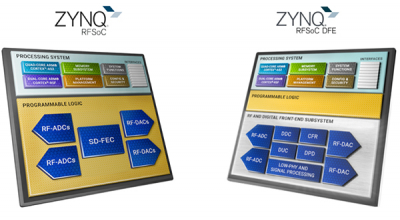

具有超宽模拟带宽的高采样率DAC和ADC是实现全数字多波段SAR系统的关键技术

本文介绍一下Xilinx公司新一代Zynq UltraScale+ RFSoC器件

本实验主要介绍使用PS端来完成ZYNQ串口打印输出的功能

本文涵盖了在 Versal GTY 和 GTYP 中使用模式生成器和检查器时对以下操作的限制

本文将演示如何在 Versal AI Core 系列 VCK190 评估套件上从 USB 辅助启动模式启动 Linux

每个模块的 GTH 规格略有不同。相比于商用级 K26C,工业级 K26I 存在一些限制

通过XTmrCtr_GetValue获取时间戳,是以时钟周期为单位的

HBM将多个DDR芯片堆叠在一起,所以也是个3D结构;每个die之间通过TVS和microbump方式连接