Vivado从此开始(进阶篇)读书笔记——综合阶段相关知识点

judy 在 周五, 10/21/2022 - 16:33 提交

对控制集百分比的说明(适用于7系列FPGA和UltraScale FPGA)如下表

对控制集百分比的说明(适用于7系列FPGA和UltraScale FPGA)如下表

本研讨会将演示如何使用可编程逻辑和 AI 引擎阵列功能对设计开展早期功能验证。

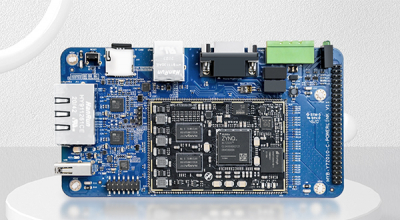

MYD-Y7Z010/20-V2开发板面向工业应用,基于FPGA+ARM架构开发

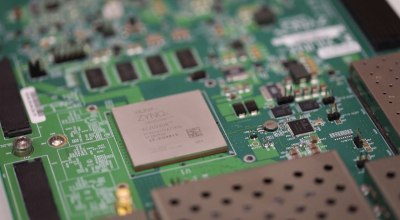

本文概述了Xilinx® Zynq® UltraScale+® RFSoC DFE的特点和产品选择。

Alveo X3 系列为多种多样的低时延交易应用同时提供了交钥匙部署和自定义实现路径。

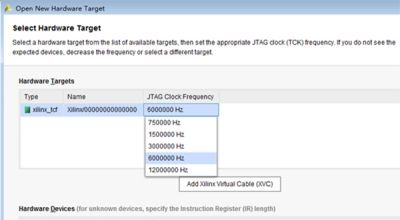

通过Vivado 自带的ibert工具可以对FPGA的GT进行板机的硬件调试。

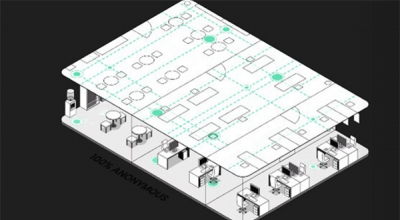

这种基于传感器的神经网络解决方案实时运行,帮助用户掌握办公室空间的占用状况以及员工的移动路径

模数转换器几乎消除了所有的模拟前端组件,射频/中频采样率高达4GHz

我们以MEMORY为例,在Vivado中可以通过下面四种方式调用FPGA中的存储单元

让我们从触发器开始,所有触发器都有一个围绕活动时钟沿的建立(setup time)和保持窗口(hold time)