【Versal DDRMC 设计咨询 】使用用户为 LPDDR4 和 x8 或 x16 DDR4 组件接口指定的 DQS 字节交换生成管脚分配时,其中可能包含错误且需更改 PCB 方可修复

judy 在 周一, 08/02/2021 - 16:30 提交

本设计咨询涵盖如下 Versal DDRMC 设计:使用对应 LPDDR4 和 x8 或 x16 DDR4 组件接口的 DQS 字节组管脚交换所生成的设计。

本设计咨询涵盖如下 Versal DDRMC 设计:使用对应 LPDDR4 和 x8 或 x16 DDR4 组件接口的 DQS 字节组管脚交换所生成的设计。

本文主要包含MultiBoot的功能简介、流程介绍和工程实现几个部分的讲解。

本视频介绍宏景智驾和赛灵思一起打造的面向高等级自动驾驶系统解决方案。

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的"成本"。 但事实总是如此吗?在本文中,我们展示了一个真实的例子

本篇博文将继续介绍在Vitis中把Settings信息传递到底层的Vivado。

本文描述如何使用 Dynamic Function eXchange 灵活高效地使用硬件资源来动态更新已部署的系统。包括对技术历史的回顾。

本视频介绍深圳市艾为智能有限公司的CMS及BSD方案

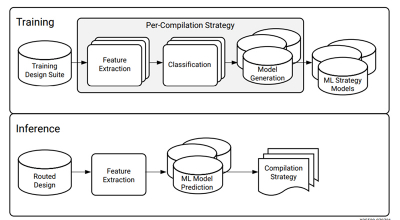

本白皮书描述智能设计如何使用机器学习和基于规则的系统来模拟时序收敛专家并提高生产力。

今天对于越来越多的人来说,人工智能(AI)已经不再是一个很“玄”的概念,而是实实在在走到了我们的身边。其中视觉AI应用就是离我们最近的一个。不论是无处不在的“刷脸”身份认证,还是工业生产线上的机器视觉检测,或者是汽车的自动驾驶,视觉AI应用正在快速渗透到我们生活中的方方面面。

Versal™Premium 系列符合 PCIe® 规范修订版 5.0,并且通过每条通道每秒 32 千兆次传输的速度支持全部链路速率。该视频演示了 Versal Premium ACAP 中面向 PCIe 的两个可用子系统,这在下一代网络和云基础架构中至关重要。