创建 Vitis 加速平台第4部分:在 Vitis 中测试定制加速平台

judy 在 周四, 11/05/2020 - 14:30 提交

在本系列博客的前几篇博文中,我们讲解了如何创建硬件和软件工程。下一步,我们将讲解如何在Vitis™中封装此工程。随后,我们将在 Vitis 中通过创建简单应用并对其进行加速,以便对该工程进行测试。

在本系列博客的前几篇博文中,我们讲解了如何创建硬件和软件工程。下一步,我们将讲解如何在Vitis™中封装此工程。随后,我们将在 Vitis 中通过创建简单应用并对其进行加速,以便对该工程进行测试。

OFweek 2020 第五届“维科杯”评选结果揭晓,赛灵思在人工智能与物联网领域“两开花”—— Vitis AI 与 Zynq SoC / MPSoC 系列产品双双获奖。其中 Vitis AI 斩获维科杯·OFweek 2020 人工智能行业优秀产品应用奖,Zynq SoC/ MPSoC 系列产品荣膺维科杯·OFweek 2020 物联网行业创新技术产品奖。

测试系统使用赛灵思 Alveo U250 加速器卡,该卡以 Mipsology 优化的领域专用架构 (DSA) 为基础。基准测试测量了我们基于 Alveo 的定制 DSA 在离线模式下以 5,011 图像/秒的速度执行基于 ResNet-50 基准的图像分类任务的效率。ResNet-50 以图像/秒为单位测量图像分类性能。

在我们所有人的生活和工作因疫情陷入困顿之际,鼓舞我们大多数人继续前行的力量来自于社会与企业合作的一个又一个鲜活的抗疫案例,他们通过各种各样的技术和创新解决方案,助力抗击新冠疫情。与此同时, 新冠疫情也激发着各种新颖应用的加速实现。在此小编想介绍几个赛灵思的客户,他们正在积极开发并交付产品与服务,帮助预防、检测和治疗新冠病毒和其他疾病:

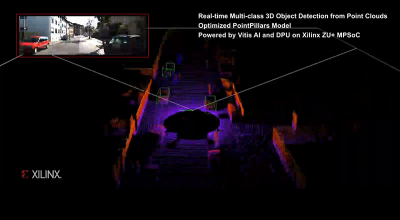

点云数据的低延迟 3D 感知对于紧凑型嵌入式系统是一个巨大的挑战。通过端到端的硬件和软件协同优化,我们能够使用 Xilinx ZU+ MPSoC 上的最新 PointPillars 模型实时运行多类 3D 检测任务。

MLPerf 组织最近发布了最新一轮机器学习性能测试结果,首次直接参加此次测试的“新力量” 赛灵思, 在最新 MLPerf 推断基准测试中取得了“图像分类”最高的性能/峰值成绩。TOPS(每秒万亿次运算) 是一个衡量性能效率的指标,意味着在给定 X 个硬件峰值计算量的情况下,赛灵思提供了最高的吞吐量性能。

ASIC 与 FPGA 的嘴仗打了十几年,在 5G 第二波商用浪潮来临之时颇有战况升级的意味。一种声音是:5G 应用的复杂性和标准的不断演进,将使 FPGA 力压 ASIC 用量;另一种声音则是:在成本和功耗压力之下,5G 基站所采用的 FPGA 平台需要向 ASIC 过渡。

Xilinx® 深度学习处理器单元(DPU)是专用于卷积神经的可配置计算引擎网络。引擎中使用的并行度是设计参数,可以根据需要选择目标设备和应用程序。它包含一组高度优化的指令,并支持大多数卷积神经网络,例如 VGG、ResNet、GoogLeNet、YOLO、SSD、MobileNet、FPN 等

刚启动MPSoC的VCU解码器时,解码器先分析码流,得到分辨率信息后再调用回调函数分配buffer。这会耗费时间,增加延迟。如果希望减少延迟,可以使用prealloc-args参数,提前指定视频分辨率信息,提前分配buffer。

5G的推出速度比之前任何一代无线技术都要快。Omdia的研究显示,5G订阅量在20年第1季度增长了四倍,超过6400万,并有望在2024年底达到100亿。就用户而言,这是4G采用率的4倍。随着5G实施的加速,它们带来了数十亿新的连接设备、数PB的额外网络流量和数百万个新的5G基站。目前全球约有7000万个基站位置。