作者:张慧娟,与非网

ASIC 与 FPGA 的嘴仗打了十几年

在 5G 第二波商用浪潮来临之时

颇有战况升级的意味

一种声音是:5G 应用的复杂性和标准的不断演进,将使 FPGA 力压 ASIC 用量;另一种声音则是:在成本和功耗压力之下,5G 基站所采用的 FPGA 平台需要向 ASIC 过渡。

5G 第二波,谁是绝佳选择?

在 5G 发展初期,技术不成熟、基站总体数量并不多,FPGA 现场可编程的优势很明显。不同于 FPGA 的灵活性,定制化的 ASIC 一旦制造完成将不能更改设计,并且初期成本高、开发周期长。根据公开数据,Xillinx 认为传统的 ASIC 设计周期平均是 14 个月,通信设备若过分依赖使用 ASIC,会让设备商的终端产品晚上市 6 个月,在 5 年内将少 33% 的利润,等于损失 14% 的市场份额。而 FPGA 可以帮助设备商快速发展原型机,快速交付,开发时间可以平均降低 55%。

2019 年末开始,局势有了些微妙变化。

随着 5G 基站数量进入爆发阶段,ASIC 方案的规模经济效应就显露出来了。

业界纷纷预测,从 2020 年第一季度开始,基站基带侧会出现 ASIC 取代 FPGA 的现象。去年底还有一个标志性事件,诺基亚宣布使用 SoC 来替代 FPGA 开发 5G 芯片组。官方解释是,之前认为 FPGA 具备可编程能力,更能满足运营商的使用需求。但是由于使用 FPGA 开发芯片推高了 5G 网络设备的单价,并且耗电量也比使用 SoC 的设备要高,所以决定取消这一计划。

种种迹象,对 FPGA 都不妙。但是 ASIC 就是绝佳选择吗?

摩尔定律到了举步维艰的地步,仅从节点的进步来提升处理的效率已经越来越困难。而测算 4G 与 5G 时代的 ASIC NRE 成本,却是几乎 3 倍的增加。另外,5G 标准仍在持续演进中,两年以上的开发周期仍是 ASIC 一大硬伤,毕竟谁也无法精准预判未来。而最为不同的一点是,5G 带来了多样性的需求,这对于以规模经济取胜的 ASIC,在某些碎片又量小的应用面前,就被缚住了手脚。

5G 第二波商用浪潮来临之际,ASIC 经济学并不可行,纯 FPGA 方案在成本与功耗方面又有掣肘。还有第三条路吗?

FPGA 的权衡之道

在第三条道路的探索上,Xilinx 进行了一次不同以往的尝试。今日发布的 Zynq RFSoC DFE,将硬化的数字前端(DFE)模块与灵活应变的可编程逻辑相结合,这也是 Xilinx 史上首次推出这样一款硬化专用 IP 多于自适应逻辑的无线电平台。

根据 Xilinx 有线与无线事业部高级总监 Gilles Garcia 的解读,这一创新旨在满足不断演进的 5G NR 无线应用标准,为了涵盖低、中、高频段频谱的广泛用例,Zynq RFSoC DFE 在采用硬化模块的 ASIC 的成本效益与可编程、自适应 SoC 的灵活性、可扩展性及上市时间优势之间,找到了技术平衡。

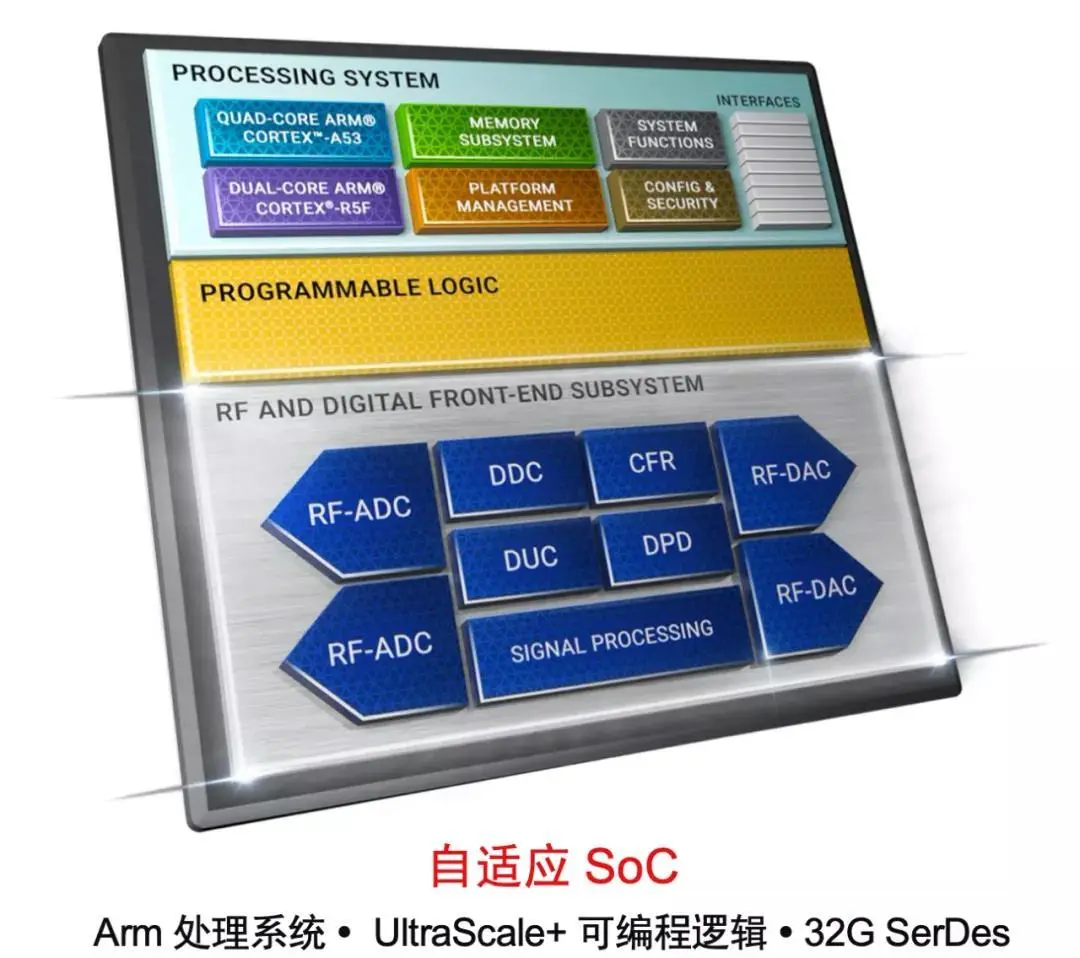

从器件架构来看,主要包括处理器子系统(四核 Arm Cortex-A53、双核 Arm Cortex-R5F)、少量的可编程逻辑单元、RF 和数字前端子系统。可以看到,在 RF 和数字前端子系统硬化的 ASIC IP 中,包括了一个完整的 DFE 模块链。

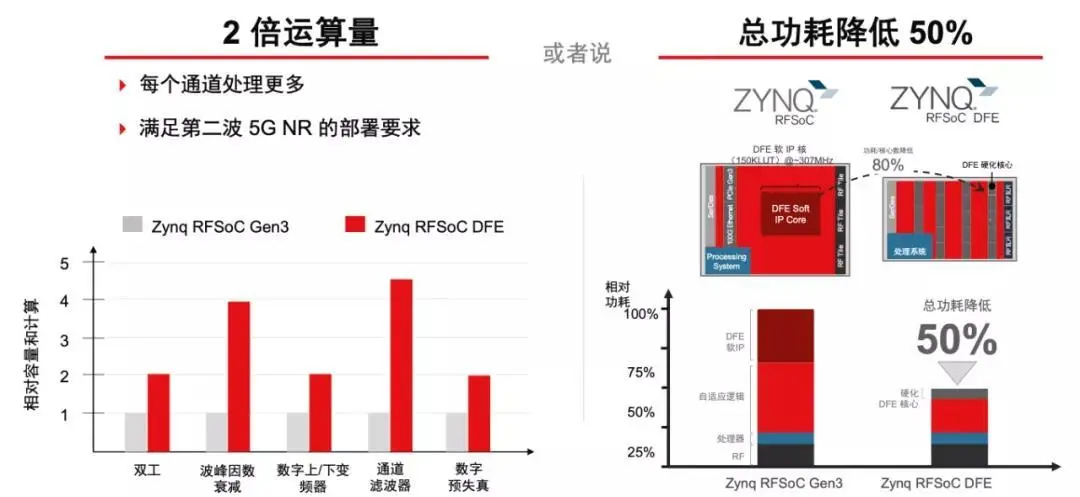

事实上,Xilinx 已经推出过三代 Zynq RFSoC 产品,在前几代产品中,这些 DFE IP 以软 IP 的形式存在于可编程逻辑单元中。而实现硬化之后,与上一代产品相比,Zynq RFSoC DFE 将单位功耗性能提升高达两倍,并且能够从小蜂窝扩展至大规模 MIMO(mMIMO)宏蜂窝。

通过在集成度和灵活性方面的权衡设计,该解决方案能够在所有 FR1 频带和新兴频带(最高 7.125GHz)内实现载波聚合/共享、多模式、多频带 400MHz 瞬时带宽。当用作毫米波中频收发器时,Zynq RFSoC DFE 可提供 1600MHz 的瞬时带宽。

在灵活性方面,支持用户绕过或定制硬化的 IP 模块,可以利用支持现有和新兴 GaN Pas 的 DPD,也可以插入其自有的 DPD IP。

5G 的多样化需求和复杂性

5G 与 4G 相比,不仅是网络带宽方面的升级,在运营管理模式上也有许多新的诉求。因此未来的网络不再是单一设备商甚至单一运营商包打天下,而是一个丰富的生态圈,因此开放性、灵活性尤为重要。

就 5G 无线电而言,所需的解决方案不仅要满足广泛部署所提出的带宽、功耗和成本挑战,还必须适应三大关键 5G 用例:增强型移动宽带(eMBB)、大规模机器类通信(mMTC)以及超可靠低时延通信(URLLC)。此外,解决方案必须能够随不断演进的 5G 标准进行扩展,如 OpenRAN(O-RAN)、全新的颠覆性 5G 商业模式。

Gilles Garcia 谈到:

5G 正在经历第二波的大规模部署,每个通道需要处理更多,需要有更高的瞬时带宽,更高的集成度水平,另外还有降低功耗,有更高的容量和更低的成本,这是设计这一款新的 Zynq RFSoC DFE 架构的初衷。而新的用例仍在不断涌现,例如虚拟现实、车联网等等,这些应用都要求低延时、低错误率,只有高度集成的类似 ASIC、但同时又可编程的平台,才可以满足这些需求。

你中有我、我中有你的新业态

在 Gilles Garcia 看来,ASIC 的经济性和可行性会随着 5G 的不断部署下降,单一方案无法满足成本、功耗、效率等多方面需求。在百万量级的无线电单元部署中,即大型的 OEM 硬件厂商中,ASIC 仍然是合适的选择。不过,5G 一个显著的趋势就是碎片化应用越来越显著,对于无线电单元量级在 50 万以下的应用中,RFSoC DFE 更有竞争力。预计 5G 在未来十年还会不断地升级,不排除一些原来采用 ASIC 战略的用户,会转向 RFSoC DFE,因为它总体置有成本更低,性能、功能更优越,还能加速上市速度。

对于未来即将发生的改变,Xilinx 不是唯一做好准备的 FPGA 厂商。

Intel 继收购 Altera 之后,于 2018 年收购了芯片公司 eASIC,该公司提供一种介于 FPGA 与 ASIC 中间的技术。通过半成品的结构化 ASIC,能够节省 NRE 费用和设计时间,而芯片的性能和功耗又接近标准单元 ASIC。此举被看作是 Intel 在 FPGA 和标准 ASIC 之间的战略布局。

相应的还有 eFPGA 的形式,例如 Achronix,Flex Logix 等厂商,通过将一个或多个 FPGA 以 IP 的形式嵌入 ASIC 或 SoC 等芯片中,实现数字可重构的结构,从而使芯片实现更高的灵活性和可重新配置的特性。

ASIC 还是 FPGA?未来的竞争边界被模糊,一方面,各自有其存在的空间和必要性,另一方面,你中有我、我中有你的新架构在萌发。如果一定要说出一个赢家,那就是混合架构的 SoC。

10月27日,AMD 和 Xilinx 联合宣布,已就 AMD 以全股票交易收购 Xilinx 达成最终协议,交易总价值 350 亿美元。更强大的产品组合呼之欲出,结合 CPU、GPU、FPGA、自适应 SoC 以及相关的软件工具,对于双方来说,这是不是都是一步好棋?

文章转载自: Xilinx赛灵思官微