从多图对比看Vivado与ISE开发流程的差异

judy 在 周二, 09/01/2020 - 09:26 提交

对 Vivado 和它的前一代设计套件,ISE 做一个组件功能上的平行比较和总结是很有用的。其目的是让那些具有在 ISE 下工作经验 (但是不具有 Vivado 下经验)的人能够更快的适应新工具的各个特性。详细信息见下表。

对 Vivado 和它的前一代设计套件,ISE 做一个组件功能上的平行比较和总结是很有用的。其目的是让那些具有在 ISE 下工作经验 (但是不具有 Vivado 下经验)的人能够更快的适应新工具的各个特性。详细信息见下表。

在本次网络研讨会上,您将了解 Vitis 环境,以及该环境如何在 Xilinx 平台上实现嵌入式软件和加速应用开发。

描述

在《Virtex UltraScale+ FPGA 数据手册》(DS923) 中,XCVU27P-3E 器件和 XCVU29P-3E 器件的最低量产软件和速度规格已从 Vivado 工具 2019.2 v1.28 更新至 Vivado 工具 2020.1.1 v1.30。

在上一期100小时从零开始:用摄像头认识世界中,暑期学校A班的同学思维巧妙,让摄像头得到了活用。本期小编继续为大家带来使用了摄像头的暑期学校B班优秀作品分享之双目视觉重建系统。让我们一起来看看吧!

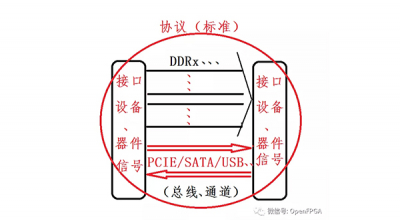

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。接口是一种连接标准,又常常被称之为物理接口。

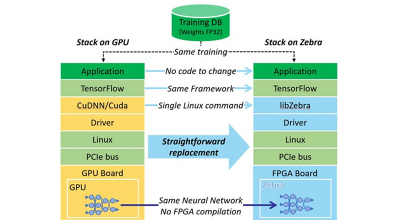

众所周知,实施一个完整的AI应用需要经历训练和推理两个过程。所谓“训练”,就是我们要将大量的数据代入到神经网络模型中运算并反复迭代,“教会”算法模型如何正确的工作

在《Zynq UltraScale+ MPSoC 数据手册》(DS925) 中,XAZU7EV-1Q 器件与 XAZU11EG-1Q 器件的最低量产软件和速度规格已从 Vivado 工具 2019.1.1 v1.26 更新至 Vivado 工具 2020.1.1 v1.30。

在市场需求和产业趋势的推动下,米尔科技携手百度,推出系列高性能及高性价比EdgeBoard 边缘AI计算卡/计算盒,助力AI项目落地。可灵活适配海量的且不断迭代的AI模型,并提供强大的运行算力。

DCT经常用来对信号进行有损数据压缩,这是由于DCT具有很强的能量集中性,大部分自然信号的能量主要集中在DCT变换后的低频部分,具体的DCT公式这里就不多推导了。二维DCT变换是在一维DCT变换的基础上,再进行一次DCT变换,二维DCT变换方法主要由三个步骤组成(信号矩阵8*8)

Versal 自适应计算加速平台 (ACAP) 是基于 TSMC 7nm FinFET 工艺技术构建的最新一代赛灵思器件。它利用高带宽片上网络 (NoC) 将代表处理器系统 (PS) 的标量引擎、代表可编程逻辑 (PL) 的自适应引擎与智能引擎有机结合在一起。本文将着重介绍智能引擎中所包含的 AI 引擎。