使用本地计算推动数字化工厂的发展:Alveo 实现的加速

judy 在 周二, 08/18/2020 - 10:07 提交

在本次网络研讨会上,您将了解 Xilinx 的 Alveo PCIe 加速卡如何在安全的本地设置下,支持数据收集、聚合、处理、建模以及人工智能指导的决策制定。您将通过卸载、加速以及直接从网络收集工厂数据,了解为什么投资 Alveo 会为您带来一种可在整个工厂车间和云端产生系统级优势的精确途径

在本次网络研讨会上,您将了解 Xilinx 的 Alveo PCIe 加速卡如何在安全的本地设置下,支持数据收集、聚合、处理、建模以及人工智能指导的决策制定。您将通过卸载、加速以及直接从网络收集工厂数据,了解为什么投资 Alveo 会为您带来一种可在整个工厂车间和云端产生系统级优势的精确途径

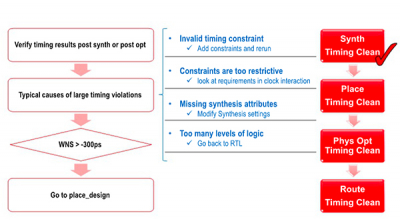

首先,我们要知道的是,Hold Time违例,是因为时钟绕的太远,到达时间太晚。而且综合之后给出的时序报告都是估计值,因此综合之后可以不考虑Hold Time,只考虑Setup Time;即便此时Hold Time违例,我们也不需要去理会

EDF文件可以直接导入Vivado,而无需Verilog源文件。

好处:

(1) 避免沙雕队友修改源代码,则可以直接提交EDF网表文件。

(2) 避免用户剽窃劳动成果,保护自己的知识产权。

(3) 对于无需更改的设计复用,直接用EDF网表会贼方便。

MAU 加速器可实现确定性的低尾时延和高吞吐量,无需在二者之间做权衡。这不仅有助于在给定的时延内使用更高质量的模型,而且还可显著节省基础架构成本并大幅降低能耗。 MAU 加速器运行在 Alveo U250 上,支持基于 ONNX 的行业标准开发流程

此参考设计是一款可配置电源解决方案,用于在各种用例中对整个 Xilinx® Zynq® UltraScale+ (ZU+) 系列MPSoC 器件进行处理。TPS65086x PMIC 拥有各种版本,因而此设计能够为从具有双核 Arm® Cortex®-A53应用处理器和双核 Arm Cortex-R5 实时处理器的基本ZU2CG 器件到更高端的 ZU7EV、ZU19EG 和ZU21DR 器件供电

本文设计了基于深度学习的人脸口罩佩戴识别系统。该方法在利用自主设计的图像识别网络以及Xilinx最新的vitis-ai技术快速开发出符合要求的系统。利用近1万个公开数据,并采用数据增强等方法,在训练后得到95%的识别准确率

该视频演示了 Xilinx IP 的平均功耗降低和数字预失真功能。

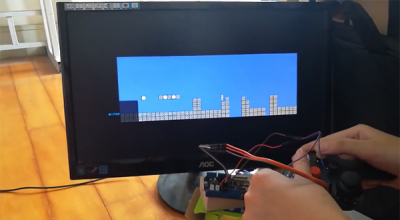

本次暑期学校,有许多优秀作品都与游戏有关。接下来,就让我们一起来看看这些有趣的“小游戏”吧!所有项目均已开源,github链接已经附上。只要根据要求设置环境,你也可以尝试这些游戏!感兴趣的读者们一定要试试哟!

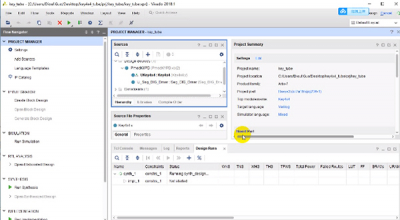

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对其进行了整理,分为了几篇文章。

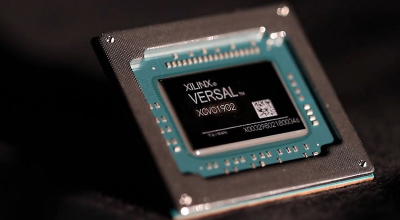

CCF ACA 2020大会8月14日上午主论坛中,Xilinx Fellow,Kees Vissers将为大家带来赛灵思ACAP架构分享。 ACAP 是赛灵思推出的高度集成的多核异构计算平台,能根据各种应用与工作负载的需求从硬件层对其进行灵活修改。