Xilinx原语详解及仿真——ODELAYE2

judy 在 周一, 12/09/2024 - 17:52 提交

7系列IO模块相关的结构如图1所示,前文对IOB、IDELAYE2、ILOGIC、OLOGIC进行了讲解,还剩下ISERDESE2、OSERDESE2、ODELAYE2原语

7系列IO模块相关的结构如图1所示,前文对IOB、IDELAYE2、ILOGIC、OLOGIC进行了讲解,还剩下ISERDESE2、OSERDESE2、ODELAYE2原语

本次项目展示了如何创建 CLI 来控制机械臂的 PWM 驱动器。还创建了一个详细的 Python 应用程序,该应用程序与 AMD MicroBlaze™ V 配合使用

以下是您需要了解的有关这些尖端半导体的所有信息,随着全球对人工智能的狂热,它们的需求也飙升。

SDRAM具有空间存储量大、读写速度快、价格相对便宜等优点。然而由于SDRAM内部利用电容来存储数据,为保证数据不丢失,需要持续对各存储电容进行刷新操作

本文使用了2024.1版本的工具,快速构建基于ZCU102的Linux及其启动镜像,并在最后简单介绍如何在Yocto里导入用户设计并修改设备树。

威视锐可编程5G网络系统(P5G)是专门用于科研5G的原型验证系统,可以搭建出一套面向卫星互联网的5G NTN端到端解决方案

常规的外差式无线电接收器已经使用了近一个世纪,如图所示。我们再次回顾一下模拟接收器的结构,以便于和数字接收器进行比较

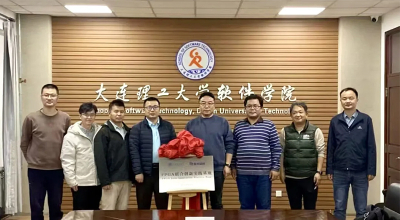

为了深化产教融合,加快推进国产FPGA人才培养,紫光同创与大连理工大学软件学院及南京信息工程大学工程训练中心达成合作,共同建设FPGA联合创新实践基地。

本文将通过PMC_GPIO作为例子来描述如何唤醒Versal系统。

3.2 规范优化了 CXL 内存设备的监控和管理,增强了 CXL 内存设备在操作系统和应用程序方面的功能