如何高效完成高速数字电路设计?参加本期研讨会马上Get

judy 在 周四, 05/14/2020 - 09:24 提交

5月22日,是德科技 (Keysight) 携手赛灵思 (Xilinx) 共同举办在线研讨会,将为您介绍针对多种应用的信号完整性仿真与设计解决方案,同时还会选取高速数字电路设计和测试中的典型应用进行分析和举例,助力您更高效的完成高速数字电路的设计和实现。

5月22日,是德科技 (Keysight) 携手赛灵思 (Xilinx) 共同举办在线研讨会,将为您介绍针对多种应用的信号完整性仿真与设计解决方案,同时还会选取高速数字电路设计和测试中的典型应用进行分析和举例,助力您更高效的完成高速数字电路的设计和实现。

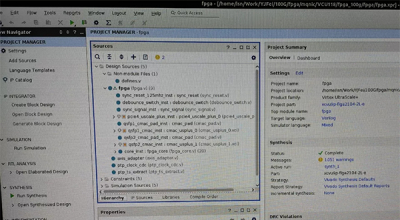

Corundum是一个基于FPGA的开源原型平台,用于高达100Gbps及更高的网络接口开发。Corundum平台包括一些用于实现实时,高线速操作的核心功能,包括:高性能数据路径,10G/ 25G / 100G以太网MAC,PCIExpress第3代,自定义PCIeDMA引擎以及本机高精确的IEEE 1588 PTP时间戳

Zynq UltraScale+ MPSoC 启动时间估算器电子表显示,QSPI 的闪存频率为 13.89MHz。如何达到该频率?

DPU-PYNQ时一个结合PYNQ框架和Vitis AI设计平台开发的全新系统覆盖层。目前主要支持 Zynq Ultrascale系列的开发板,如Ultra96、ZCU104和ZCU111。PYNQ系列用户可以通过PIP指令一键将PYNQ2.5镜像升级到支持DPU的版本,纯软件安装包更新的体验!

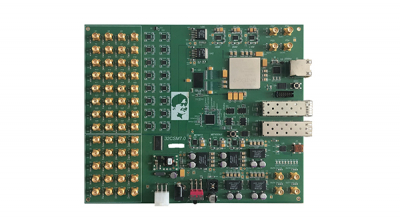

本篇的内容基于jesd204b接口的ADC和FPGA的硬件板卡,通过调用jesd204b ip核来一步步在FPGA内部实现高速ADC数据采集,jesd204b协议和xilinx 的jesd204 IP核相关基本知识已在前面多篇文章中详细介绍,这里不再叙述~

Xilinx 提供基于命令行的实用工具 xbutil,它可用来与 Xilinx 加速器卡的用户功能进行交互。本视频将带您了解使用 xbutil 检查、报告并验证 Alveo 卡的基本步骤

作者:付汉杰,hankf@xilinx.com,文章转载自:

该演示说明了如何使用 Vitis™ IDE 进行软件性能分析。

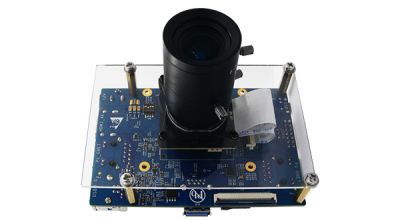

随着现代图像及视频处理技术的不断发展,人们对图像处理提出了新的要求,最近几年,图像的分辨率和扫描频率都有了较大范围的提升,1080P分辨率的视频已经非常流行,2K甚至4K分辨率的图像也在火热发展中。基于软件的图像处理方法存在着一些局限性,尤其是计算速度和算法效率方面

心跳包就是在客户端和服务器间定时通知对方自己状态的一个自己定义的命令字,按照一定的时间间隔发送,类似于心跳,所以叫做心跳包。心跳包在GPRS通信和CDMA通信的应用方面使用非常广泛。数据网关会定时清理没有数据的路由,心跳包通常设定在30-40秒之间。所谓的心跳包就是客户端定时发送简单的信息给服务器端告诉它我还在而已