【生态圈】告别缓冲等待,赛灵思对“爱奇艺崩了”事件说 No

judy 在 周一, 03/02/2020 - 13:35 提交

2 月 16 日晚 8 点左右,众多用户反馈爱奇艺 APP 出现崩溃情况,无法正常观看。随后#爱奇艺崩了#一度成为网络热搜。一同上热搜的,还有“韩剧 TV 崩了”、“小米电视崩了”。与此同时,来自 QuestMobile 的数据显示,2020 年春节假期后移动视频的日均活跃用户增量从放假前的 16% 增长至 36% 。

2 月 16 日晚 8 点左右,众多用户反馈爱奇艺 APP 出现崩溃情况,无法正常观看。随后#爱奇艺崩了#一度成为网络热搜。一同上热搜的,还有“韩剧 TV 崩了”、“小米电视崩了”。与此同时,来自 QuestMobile 的数据显示,2020 年春节假期后移动视频的日均活跃用户增量从放假前的 16% 增长至 36% 。

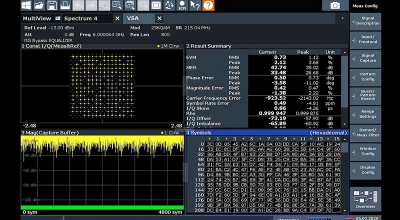

该视频展示了使用 16T16R ZCU216 评估套件在 6 GHz 频率下 RF-DAC 和 RF-ADC 的出色性能。

本指南介绍赛灵思 Alveo™ 数据中心加速器卡的解包、安装和启动。

IO管脚约束是FPGA设计上板验证的必需环节,它们会对布局布线和时序造成影响。有三种方式来进行管脚约束,一种是通过VIvado管脚约束界面,一种是通过命令行,还有一种可以导入CSV文件

由于XDC约束是按顺序应用的,并且基于明确的优先级规则进行优先级排序,因此必须仔细检查约束的顺序。如果多个物理约束发生冲突,则最新约束将获胜。 例如,如果通过多个XDC文件为I / O端口分配了不同的位置(LOC),则分配给该端口的最新位置优先。

基于闪存技术的Xilinx CPLD具有较低的逻辑密度,功耗也比较低。为了提高逻辑密度、集成更多功能,PLD厂商的每一代器件都会采用当前最新的工艺技术。不同的功能需求以及集成工艺,使得PLD的供电电压有所不同。

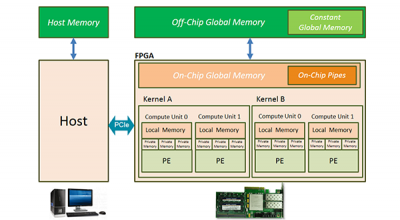

在OpenCL中提供的存储模型中,有如下几种Memory类型。Host Memory:Host Memory指的是连接在主板上的内存条,仅供host进行数据读取。Off-Chip Global memory:Off-Chip Global memory 指的是在FPGA板卡上通过硬件与FPGA芯片连接的内存条。数据存取所花费的时间相对较长,但是容量相对较大。

Zynq的开发四种方式:纯PL开发,纯PS开发(helloworld),PS+PL(无操作系统,跑裸跑程序),PS+PL(跑操作系统)。

所有市场的安全性都变得越来越重要。在Zynq®UltraScale +™平台上使用受信任的执行环境(TEE),通过将关键安全性元素与系统其余部分隔离开来,可以提供主要的安全优势。

什么是XPM?可能很多人没听过也没用过,它的全称是Xilinx Parameterized Macros,也就是Xilinx的参数化的宏,跟原语的例化和使用方式一样。可以在Vivado中的Tools->Language Templates中查看都有哪些XPM可以例化。