【下载】Alveo U280 ES1 数据中心加速器卡用户指南 (中文版)

judy 在 周二, 08/27/2019 - 10:51 提交

本文详细介绍了 Alveo™ U280 数据中心加速卡,它是采用了 Xilinx® Virtex® UltraScale+™ 技术的标准 PCIe® (Peripheral Component Interconnect express) Gen3 x16 加速卡。

本文详细介绍了 Alveo™ U280 数据中心加速卡,它是采用了 Xilinx® Virtex® UltraScale+™ 技术的标准 PCIe® (Peripheral Component Interconnect express) Gen3 x16 加速卡。

Xilinx 推出全球容量最大的 FPGA - Virtex® UltraScale+™ VU19P,不仅能实现当今最先进 ASIC 和 SoC 技术的原型与模拟设计,还能支持各种复杂的新兴算法。

前面我们已经学习了TCP的所有发送、接收和各种回调函数。本文将介绍最后一部分,TCP的轮询机制。在前面TCP发送Hello World的实例中,我们是在main函数的while循环中每隔1s调用一次数据发送函数。本文的实例将利用轮询机制完成同样的功能。

今天是OpenPOWER基金会历史上最重要的日子之一。伴随着IBM宣布对开源社区的新贡献,包括开源POWER指令集架构(ISA)与在2019 OpenPOWER北美峰会上公布的关键硬件参考设计,POWER架构的未来从未如此光明。

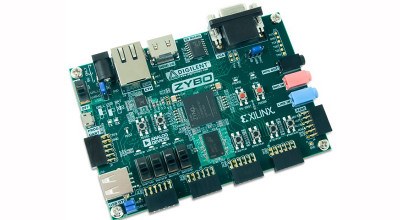

ZYNQ内部的总体框架如所示,PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及Memory接口。PS和PL的相互通信通过两个通路完成,分别是GP(General Purpose)Ports和HP(High Performance)Ports。GP Ports包含2个Master接口和2个Slave接口,符合标准的AXI协议数据位宽是32bit。HP Ports包含4个接口,全部是PL作为Master

2019年8月19日到21日,第31届Hot Chips大会在斯坦福大学成功举办。 本次大会确实是有非常多非常扎实的工作,也展现了整个处理器与高性能芯片领域行业的趋势与变化。本系列文章将介绍我在Hot Chips大会上的几点观察与思考,涵盖以下几点内容:

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1。打开Vivado,创建一个名为design_test的空白工程。点击Add source或者Sources中的+号来添加或者创建一个设计源文件,点击Next。

本课程介绍如何在边缘计算平台上使用DNN算法、模型、推理、训练以及框架。

本篇从hello world开始,简要介绍驱动的基本结构,然后再进一步介绍LED硬件的搭建,以及驱动的编写,设备树的修改。让大家对linux驱动有一个基本的认识。

在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。Xilinx Vivado集成设计环境(IDE)时序引擎使用ClocK特征计算时序路径要求,并通过松弛计算报告设计时序裕度(Slack)。