FPGA难懂?与GPU类比一下就明白了

judy 在 周三, 08/21/2019 - 09:50 提交

FPGA 是一堆晶体管,你可以把它们连接(wire up)起来做出任何你想要的电路。它就像一个纳米级面包板。使用 FPGA 就像芯片流片,但是你只需要买这一张芯片就可以搭建不一样的设计,作为交换,你需要付出一些效率上的代价

FPGA 是一堆晶体管,你可以把它们连接(wire up)起来做出任何你想要的电路。它就像一个纳米级面包板。使用 FPGA 就像芯片流片,但是你只需要买这一张芯片就可以搭建不一样的设计,作为交换,你需要付出一些效率上的代价

前两篇我们学习了TCP的发送,本文学习如何处理接收数据。本文使用TCP设计一个echo服务器,开发板将来自所有IP地址和端口的数据原路发送回去,功能和本系列第15篇的UDP echo服务器相同。本文实例与SDK提供的“lwip echo server”例程相比要简化许多,没有使用DHCP协议。本文主要是学习TCP的接收回调,DHCP的内容会在后面专门讲述。

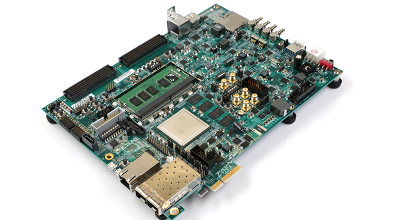

VCU 模块在PL侧,一共有五个AXI接口,它们分别是两个 Encoder AXI,两个 Decoder AXI, 和一个 MCU AXI。两个 Encoder/Decoder 的 AXI 接口必须都连接到 MPSoC PS,即使只用一路编码,或者一路解码

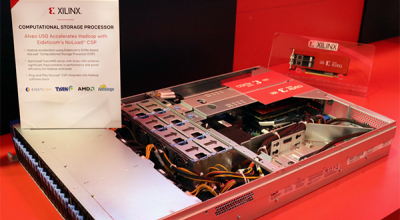

赛灵思 Alveo™ U280 数据中心加速器卡支持 PCI Express® Gen3 x 16 和 Gen4 x 8,配备 8 GB 高带宽存储器 (HBM2),旨在加速计算密集型应用,如机器学习、数据分析和视频处理存储器限制、计算密集型应用包括数据库分析和机器学习推断

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

Zynq器件将arm和FPGA结合,利用了两者各自的优势,arm可以实现灵活的控制,而FPGA部分可以实现算法加速,这大大扩展了zynq的应用。比如深度学习加速,图像处理等等。PL侧表示FPGA的逻辑部分,PS侧为arm端以及一些AXI接口控制部分,二者实际上通过AXI接口实现通信和互联

一个项目看上去很简单,精心设置了架构,结果越做发现冲突越多,直到整个逻辑完全混乱。本来一天可以的完成的事不知道怎么搞的一个星期还没有完成;本来只需要做一行更改,结果却涉及到N个模块;出现了一个非常小的BUG打了一个补丁

对赛灵思而言,上星期是激动人心的一个星期。业界首款半高半长、可支持 PCIe Gen 4 的自适应加速器卡Alveo U50 正式发布。长约7英寸,宽约2英寸,Alveo U50是小型封装的一大突破。该卡集成 HBM2 高带宽存储器、100Gbps 网络连接和赛灵思 UltraScale+ FPGA 架构

2019Xilinx暑期学校全记录

在这篇文章里你可以了解到广告推荐算法Wide and deep模型的相关知识和搭建方法,还能了解到模型优化和评估的方式。我还为你准备了将模型部署到FPGA上做硬件加速的方法,希望对你有帮助