用LUT来搭建乘法器

judy 在 周五, 08/16/2019 - 13:32 提交

卷积占据了CNN网络中绝大部分运算,进行乘法运算通常都是使用FPGA中的DSP,这样算力就受到了器件中DSP资源的限制。比如在zynq7000器件中,DSP资源就较少,神经网络的性能就无法得到提升。利用xilinx器件中LUT的结构特征,设计出的乘法器不但能灵活适应数据位宽,而且能最大限度降低LUT资源使用

卷积占据了CNN网络中绝大部分运算,进行乘法运算通常都是使用FPGA中的DSP,这样算力就受到了器件中DSP资源的限制。比如在zynq7000器件中,DSP资源就较少,神经网络的性能就无法得到提升。利用xilinx器件中LUT的结构特征,设计出的乘法器不但能灵活适应数据位宽,而且能最大限度降低LUT资源使用

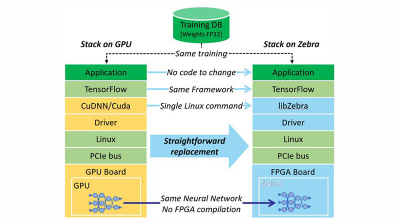

Zebra 可消除深度学习推断中具有挑战性的编程及 FPGA 任务。Zebra 可轻松部署和适应广泛的神经网络及框架。

AXI GPIO模块将PL端连接的GPIO信号通过AXI接口与PS模块连接,PS通过AXI接口的地址映射对PL端的GPIO信号进行读写等控制。与EMIO可以实现相同的功能,区别主要在于EMIO对于少数GPIO接口进行单独的控制,而AXI GPIO可以对多个GPIO接口合并成的总线进行整体读写控制。

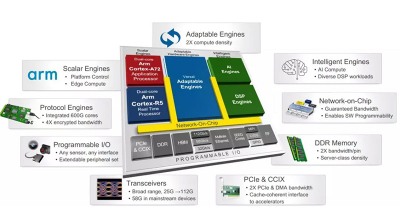

ACAP是Xilinx推出的一种革命性异构计算架构,计划在今年10月份推出。它将标量计算,可编程逻辑还有矢量计算结合在一起,充分利用各自的优势,不仅仅增强了针对各种机器学习算法的适用性,也提高了计算密度和存储带宽。其中AI engine和NoC是新颖的设计,FPGA和CPU的结合早在zynq系列中已经应用

上文介绍了用TCP发送“Hello World”的实例,工作在client模式下。本文实现同样的功能,但让TCP工作在server模式下。把开发板当作服务器,远程主机为客服端访问服务器,实现被动连接。TCP client和TCP server在lwIP中的连接流程和区别可参考本系列前面与lwIP相关的文章

2019年8月1日至2日,“中国开放指令生态(RISC-V)联盟”(简称CRVA联盟)与鹏城实验室,在湖北恩施举行的中国计算机学会第二十三届计算机工程与工艺学术年会暨第九届“微处理器技术”论坛(NCCET 2019)现场,联合展示了最新研发的RISC-V开源芯片设计系统级验证及原型平台SERVE,介绍开源理念并鼓励参会人员积极参与。

一、IP封装:1、打开Vivado,点击Create Project。2、点击Next,在Project name中输入我们的项目名称:74LS00。3、点击Next,默认勾选Do not specify…4、点击Next,核对信息,然后点击Finish。5、在空白工程中,左侧Flow Navigator中,选择PROJECT MANAGER下的Add Source。

Vitesse Data 的 Deepgreen DB 是一款可扩展的 MPP 数据库解决方案,源于开源 Greenplum 数据库项目,与开源项目完全兼容。 Deepgreen DB 可在本地设备或公共云上无缝工作。AWS F1 实例可使用多达 8 个 FPGA 实例针对总共 64 vCPU 和 976 GB 的内存进行配置。

以交换机设计为例。在交换机设计前期,转发表项是固化在交换机内部的(给FPGA片内BRAM初始值),但是在测试过程中,往往需要对表项进行修改,如果直接修改BRAM的coe文件,则需要重新综合、实现、生成bit文件,其中,综合与实现耗时十分严重,设计规模越大,消耗的时间越长,而生成bit文件消耗的时间则相对固定

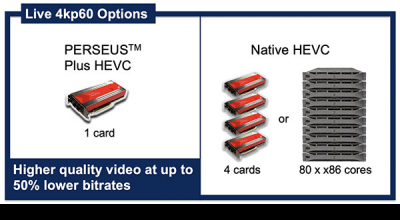

PERSEUS Plus 是一项独特的视频编码技术,可显著提高任何标准编码器(如 AVC/H.264、HEVC、VP9以及未来的 AV1)的质量和吞吐量。广泛的设备都支持回放,因为回放采用现有底层编解码器的硬件解码功能。与 Xilinx FPGA 结合使用时,PERSEUS 可提供市场上密度最高的编码解决方案,支持在单个卡上使用现场 4kp60 编码等