【重磅】GCC和CCIX宣布合作,共推异构缓存一致性加速架构

judy 在 周一, 04/15/2019 - 11:57 提交

2019年4月8日,绿色计算产业联盟(GCC)和CCIX 联盟(CCIX)宣布双方签订了合作备忘录,支持CCIX 作为统一的互联技术工业标准,及GCC 服务器标准参考指南的核心要求。通过此次合作,GCC 和CCIX 将共同推动CCIX 技术在服务器生态系统中的认知和采用

2019年4月8日,绿色计算产业联盟(GCC)和CCIX 联盟(CCIX)宣布双方签订了合作备忘录,支持CCIX 作为统一的互联技术工业标准,及GCC 服务器标准参考指南的核心要求。通过此次合作,GCC 和CCIX 将共同推动CCIX 技术在服务器生态系统中的认知和采用

Vivado不支持即时分析有矛盾的时序异常,需要运行report_exceptions进行完整的分析,报告所有时序异常。多周期路径的情况有很多,比较复杂,单独放在第35篇中讲述。本文介绍其余三种时序异常的相关知识。

【干货分享】Get到这些小技巧,FPGA设计将提高一个台阶

Zynq® UltraScale+™ RFSoC 集成 RF 采样数据转换器和 SD-FEC 硬 IP 模块,可提供一个能够满足 5G NR 解决方案重要尺寸及功耗需求的、灵活应变的单片无线电解决方案。

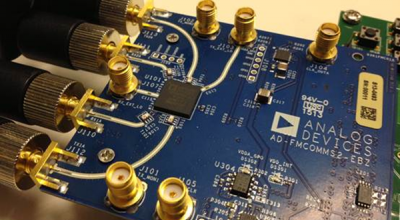

JESD204B是一种新型的基于高速SERDES的ADC/DAC数据传输接口。随着ADC/DAC采样速率的不断提高,数据的吞吐量也越来越大,对于500MSPS以上的ADC/DAC,动辄就是几十个G的数据吞吐率,而采用传统的CMOS和LVDS已经很难满足设计要求,这个时候,JESD204B应运而生。现在各大厂商的高速ADC/DAC上基本都采用了这种接口

为了能让工程师尽快掌握最新的开发工具Vivado,加速产品更新及上市进程,依元素科技推出为期2天的Vivado高级培训班。培训中不仅有丰富的理论知识,还带有配套的动手实验和案例分析,通过理论与实践相结合,使学员能有效快速地掌握基于Vivado开发工具的设计流程及其设计技巧

Xilinx AI 解决方案专家李达昌分享《基于赛灵思机器学习解决方案的视频分析应用》

介绍 Vivado® HLS 工具从 C 语言设计中抽象出来的端口级 AXI 接口协议。

作者:liuyayong

1、实验方案

图1 实验方案系统框图

2、具体步骤

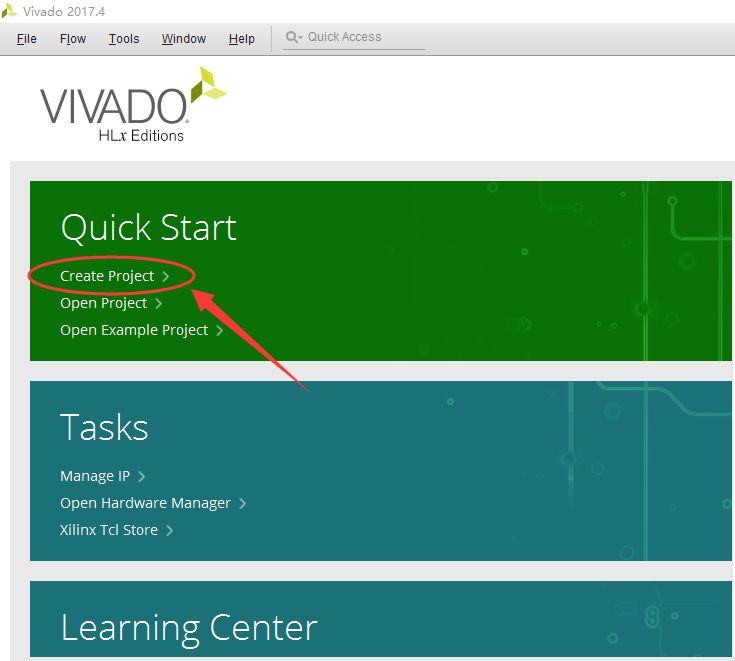

2.1、vivado工程建立

①打开vivado集成开发环境,点击“Create Project”,如下图所示。

②点击“Next”,如下图所示。

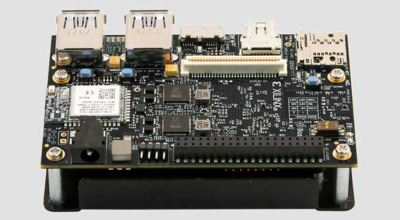

安富利在成功推出其Ultra96开发板仅一年后,再次发布新的Ultra96-V2,为工业级人工智能(AI)和物联网(IoT)应用提供动力。安富利的Ultra96-V2配备了更新的无线电模块,使工程师能够将业务扩展到新市场,是智能家居、汽车、工业控制和许多其他应用的理想平台。