ZYNQ+Vivado2015.2系列(十二)按键中断(PL中断请求)

judy 在 周三, 12/26/2018 - 14:39 提交

PS和PL之间的交互,怎么都逃不过中断,稍微大型的数字系统,PS和PL之间配合使用就需要中断作为桥梁。本文通过按键发起中断请求尝试学习PL请求中断的处理机制。

PS和PL之间的交互,怎么都逃不过中断,稍微大型的数字系统,PS和PL之间配合使用就需要中断作为桥梁。本文通过按键发起中断请求尝试学习PL请求中断的处理机制。

VCU128 开发板采用全新 Xilinx VU37P HBM FPGA,利用堆叠芯片互连将 HBM 裸片添加到封装基板上的 FPGA 裸片旁边。支持高带宽存储器(HBM) 的 Xilinx FPGA 是计算带宽问题(与在 PCB 上使用 DDR4 等并行内存相关)的最优解决方案

赛灵思业经验证的 5G 网络解决方案以及丰富的生态系统可以加速前瞻性的 5G NR 网络的部署和管理,包括智能网络遥测, AI/ML 工具, SoN 等,同时还可实现网络的无缝升级,从而满足那些新兴的标准和算法的更迭。我们诚挚地邀请您光临赛灵思在 2019 年世界通信移动大会(MWC 2019)上的展位,体验赛灵思的芯片、IP 和工具如何帮助客户打造灵活应变、智能、领先的 5G 系统

从工厂自动化的操作面板到医患监护系统,物联网正改变着所有类型的人机界面(HMI),并因而将网络安全和功能安全,以及混合了云端和本地断的数据扩展至所有这些可视化的信息交互节点。

篇主要介绍PCIe总线的复位方式。

环境准备

首先肯定是要下载xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin文件,这是官方提供的linux下交叉编译链安装文件,下载地址为:https://pan.baidu.com/s/1eSP85nO 。

安装交叉编译环境工作:

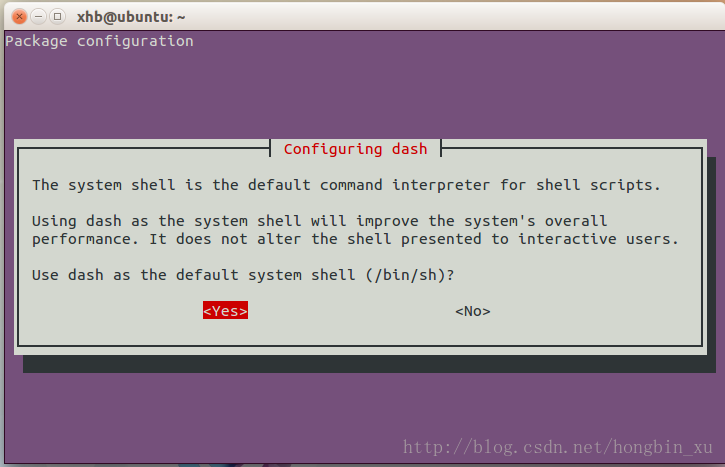

1、由于安装文件只能在bash下运行,所以要将dash改为bash,输入以下指令:

sudo dpkg-reconfigure -plow dash

选择No,切换到bash。

2、建立一个文件夹作为安装路径;

我的指定的安装目录为:/opt/cross_compiler

Bigstream 在 XDF 硅谷 2018 展示无缝超加速

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。ZYNQ的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲

Zynq在PS和PL之间有9个AXI接口。 在PL方面,有4x AXI Master HP(高性能)端口,2x AXI GP(通用)端口,2x AXI Slave GP端口和1x AXI Master ACP端口。 PS中还有连接到PL的GPIO控制器