PCIx系列之“PCIe总线复位”

judy 在 周二, 12/25/2018 - 15:08 提交

篇主要介绍PCIe总线的复位方式。

篇主要介绍PCIe总线的复位方式。

环境准备

首先肯定是要下载xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin文件,这是官方提供的linux下交叉编译链安装文件,下载地址为:https://pan.baidu.com/s/1eSP85nO 。

安装交叉编译环境工作:

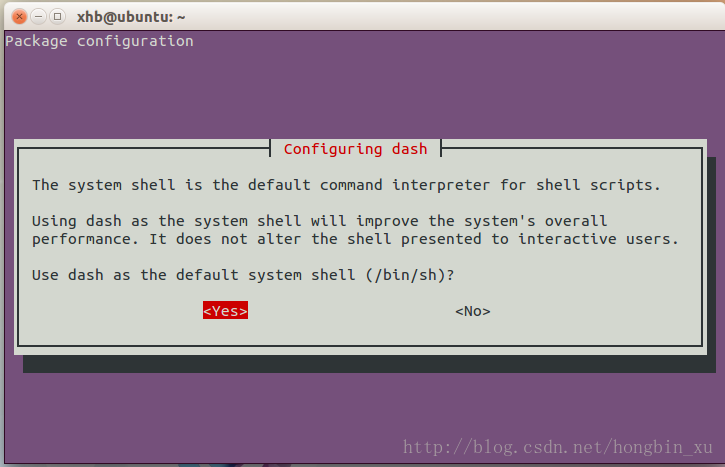

1、由于安装文件只能在bash下运行,所以要将dash改为bash,输入以下指令:

sudo dpkg-reconfigure -plow dash

选择No,切换到bash。

2、建立一个文件夹作为安装路径;

我的指定的安装目录为:/opt/cross_compiler

Bigstream 在 XDF 硅谷 2018 展示无缝超加速

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用

Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。ZYNQ的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲

Zynq在PS和PL之间有9个AXI接口。 在PL方面,有4x AXI Master HP(高性能)端口,2x AXI GP(通用)端口,2x AXI Slave GP端口和1x AXI Master ACP端口。 PS中还有连接到PL的GPIO控制器

Mipsology 为深度学习推断开发了最先进的基于 FPGA 的计算引擎。它可以无缝地替换 GPU / CPU 来处理一般或定制的神经网络,具有极高的吞吐量、易用性和零更改性。

本片主要介绍PCIe总线的电源管理,主要包括不同板卡的功耗、板卡的能耗等级等。

如果您有一个好创意,但却对于将要使用的软硬件知识没多少概念,怎么办? 马上报班一项项开始学习,还是想办法找到一个简单易用并合适的工具?

PYNQ-Z2的硬件平台以Xilinx ZYNQ SoC为核心,而Arm与FPGA的异构系统是创建高性能嵌入式系统应用的基础也是与市面上众多嵌入式平台最大的不同之处。本台有别于一般传统的ZYNQ开发平台,PYNQ-Z2支持Python 语言开发,同时也可以采用传统的Xilinx Vivado 开发工具流程平台开发嵌入式系统应用