JESD204B数据链路建立过程

judy 在 周四, 10/24/2024 - 09:41 提交

本文主要讲述JESD204B子类一的数据链路建立过程,后文讲解JESD204三种子类模式的链路建立,进而理解各种子类实现确定性延迟的方式。

本文主要讲述JESD204B子类一的数据链路建立过程,后文讲解JESD204三种子类模式的链路建立,进而理解各种子类实现确定性延迟的方式。

具有先进安全特性的FPGA可作为计算机系统中高效的硬件可信根(HRoT),提供防篡改组件,确保安全性和完整性

Xilinx®7系列FPGA集成了新一代PCI Express集成块,支持8.0Gb/s数据速率的PCI Express 3.0。本文介绍了7系列FPGA PCIe Gen3的应用接口及一些特性。

例化两个UDP协议栈模块,分别为主机A和主机B,主机A将用户端输入的数据打包,通过GMII接口发送给主机B

本文基于此解释了卷积神经网络(CNN)及其对人工智能和机器学习的意义。

本文以实际案例分析的方式来揭示合规性测试、互操作性测和实现方法

本文探索FPGA在推动网络边缘AI创新方面的重要作用。

珠海錾芯半导体基于自有EDA软件ZESTOPT显著提升Transformer硬件PPA(Power, Performance, Area)

今天分享下数字信号处理中的“有限字长效应”。

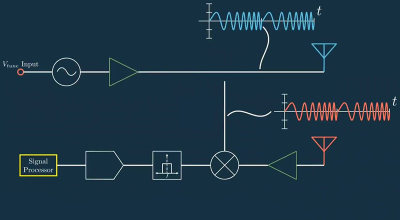

调频连续波(FMCW)雷达是现代汽车驾驶辅助系统的核心技术,包括自适应巡航控制、车道偏离警告和盲点监测等功能