开发者分享 | 使用方法论报告 3:时序已满足,但硬件中存在 DDR4 校准失败

judy 在 周四, 09/02/2021 - 14:59 提交

本篇博文中的分析是根据真实客户问题撰写的,该客户发现硬件中存在 DDR4 校准错误,不同板以及不同构建 (build) 之间出现的故障并不一致。本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本篇博文中的分析是根据真实客户问题撰写的,该客户发现硬件中存在 DDR4 校准错误,不同板以及不同构建 (build) 之间出现的故障并不一致。本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

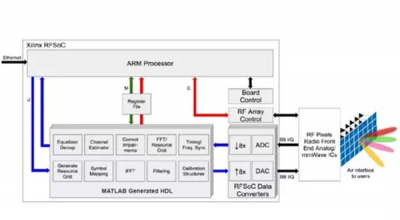

新兴的 5G 网络依托毫米波频谱运行,这意味着 5G 网络的性能优于 4G 网络,能够以更高的速度、更低的延迟传输更多数据。毫米波频谱技术发展前景广阔,但也使设备制造商面临大量设计挑战。例如,相比低频信号,毫米波频谱信号更易因大气及其他物体的阻隔而衰减。

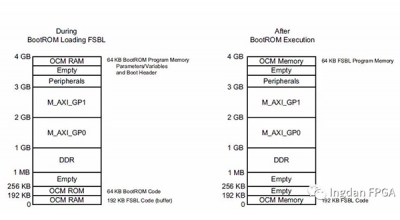

在一些工业应用中不管出于成本还是功耗又或者集成难度可能不需要DDR,这些系统只需要很小的内存空间来存储和执行其应用程序,对于这些系统OCM可以满足其与存储器相关的需求。本文主要介绍在OCM空间不足时从flash执行应用程序时如何提高性能。

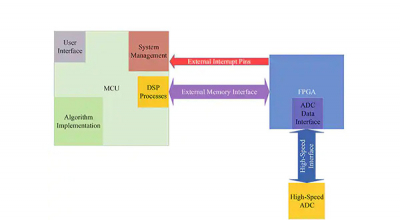

本文重点介绍分立式微控制器 (MCU) 和分立式现场可编程门阵列 (FPGA) 的组合,展示了这种架构如何适合高效和迭代的设计过程。利用研究资料、实证结果和案例研究,探讨这种架构的好处,并提供示范性的应用。读完本文,嵌入式系统设计者将对何时以及如何实现这种多功能硬件架构有个更好的理解

BittWare的SmartNIC Shell和BittWare的Loopback Example的功能之一是一个数据包解析器/分类器,它可以从数据包中提取协议字段。通过这篇白皮书,我们不仅要描述我们的Parser,还要解释如何使用HLS来构建和配置它,从而获得比使用P4语言更好的实现。

本篇博文中的分析是根据真实客户问题撰写的,该客户发现不同操作系统间 QoR 性能存在差异。虽然可以理解赛灵思无法保证不同操作系统间的可重复性,正如"赛灵思答复记录 61599"中所述,但此处案例中出现的差异量级值得进一步深入调查。

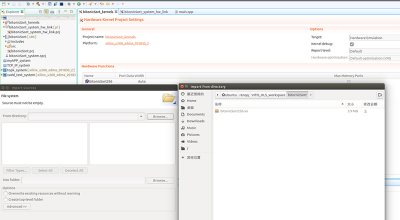

HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗?

自动化可重复的工作、自主做出复杂决定,机器人正借由效率的提升持续改变着未来工作模式。机器人适应环境变化的能力越强,其所能提供的价值就越大。为什么固定功能芯片已难以满足机器人行业需求?

本篇博文中的分析是根据客户真实问题撰写的,该客户发现即使时序已得到满足的情况下,硬件功能仍出现错误。最后发现,问题与时钟域交汇 (Clock Domain Crossing) 有关,因此,本篇博文介绍了如何调试设计中的时钟域交汇问题。

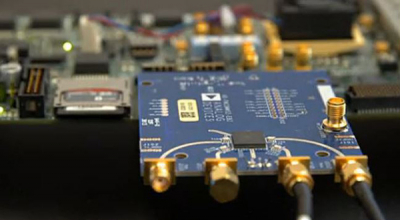

本文阐释了JESD204B标准的ADC与FPGA的接口,如何判断其是否正常工作,以及可能更重要的是,如何在有问题时排除故障。文中讨论的故障排除技术可以采用常用的测试与测量设备,包括示波器和逻辑分析仪,以及Xilinx的ChipScope或Altera的SignalTap等软件工具。同时说明了接口讯号传输,以便能够利用一种或多种方法实现讯号传输的可视化。