用于 LiDAR 的 Zynq UltraScale+ MPSoC 系统级模块

judy 在 周二, 11/15/2022 - 16:18 提交

Zynq UltraScale+ MPSoC 器件实现了基于 SoC 的自适应产品设计,这给 LiDAR 应用实现带来了非常大的前景

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

Zynq UltraScale+ MPSoC 器件实现了基于 SoC 的自适应产品设计,这给 LiDAR 应用实现带来了非常大的前景

本文详细介绍了一种实现FIPS 140-3认证的SEE的方法。

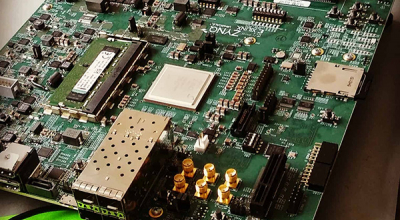

徕卡CityMapper-2是徕卡测量系统使用Enclustra Mercury+ XU8模块和FPGA Manager PCIe IP解决方案

由于UG1029已经对LINUX下dfu-util的操作步骤做了详细说明,本文介绍WIN10下dfu-util的操作步骤

该演示涵盖了时间敏感网络 (TSN) 的基本特性、TSN IP 核的特性以及内核支持的流量类别。

与众多其他行业一样,广播商和内容制作商的工作流也受到了思维模式变化带来的影响

本文将探讨如何以 Zynq UltraScale 器件上的 IP 核为目标,使用 Python 来创建一些强大的应用和实用工具。

Zynq UltraScale+ 的目标参考设计为经过全面验证的设计模块提供单独的知识产权和系统基础架构块

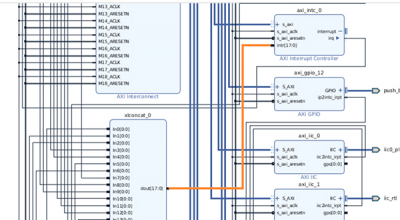

本篇博文主要讲解在 PL 中从 IP 核到 PS 之间需要完成含超 16 次中断的布线的情况下,该如何使用 AXI Interrupt Controller (INTC)

本文主要着重介绍了两个方面:如何从源码工程构建编译生成镜像文件和如何快速运行demo工程。