Versal家族到底都有哪些兄弟姐妹

judy 在 周五, 05/20/2022 - 13:41 提交

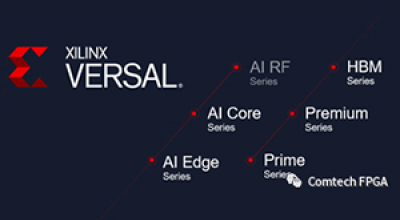

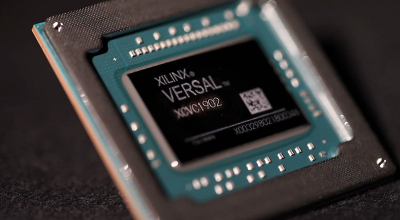

面向不同应用,Versal家族有AI Core, AI Edge , AI RF,Prime, Premium,HBM,六个系列、名字看起来是不是十分复杂?今天让我们来和您好好唠唠Versal系列这兄弟姐妹六系列!

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

面向不同应用,Versal家族有AI Core, AI Edge , AI RF,Prime, Premium,HBM,六个系列、名字看起来是不是十分复杂?今天让我们来和您好好唠唠Versal系列这兄弟姐妹六系列!

在Vivado里,可以从Block Design导出TCL脚本,保存工程。之后可以从TCL脚本恢复工程。导出的TCL脚本中,可能不包含用户IP的路径信息

SEM IP在上板调试过程中有时会出现一些错误, 比如无法执行IP的插错纠错功能; 或者自身的初始化无法完成等等, 需要对SEM IP本身进行调试定位

以下是在 Vitis™ 软件平台中创建 Platform Loader and Manager (PLM) elf 文件的步骤。在 Versal™ 器件中,PLM 在 PMC 内执行,并用于引导 APU 和 RPU。

时间敏感型网络( TSN )是工业自动化领域的一项重大进步,通过标准以太网连接提供确定性的时间敏感型功能。TSN 能够确保大规模工业网络的数据在需要的位置和时间完成传送。

在 AMD,我们对 Versal® ACAP 所搭载的 AI 引擎技术感到兴奋不已,因为在 AMD 和赛灵思服务的众多市场上,其对交付高性能自适应计算起到重要作用。

市售常见的基于FPGA的平台产品包括FPGA开发板、FPGA原型验证系统。既然他们同样都是基于FPGA芯片设计的,为什么规模、功能、成本和价格上有非常大的差异?

Ubuntu20.04LTS中使用Vivado 2021.2时,每次重启Vivado,文本编辑界面的字体大小就会变成默认大小。

本章旨在演示如何基于 Versal™ 来构建同时使用 SmartLynq+ 模块和高速调试端口 (HSDP) 的系统。

本章演示了如何利用 Vivado® 工具并使用 PL AXI GPIO 来创建嵌入式设计。其中还演示了如何在 Versal 器件上为基于 Arm® Cortex™-A72 核的 APU 配置并构建 Linux 操作系统。