【工程师分享】VCK190 PCIe QDMA 通用数据传输参考设计

judy 在 周四, 03/24/2022 - 14:20 提交

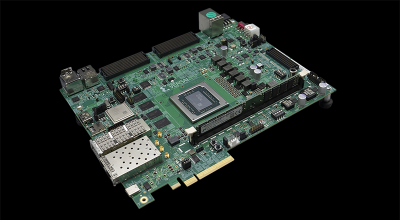

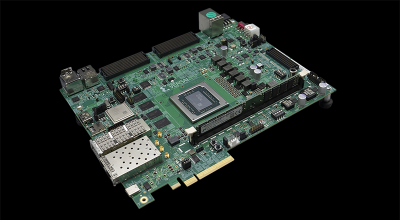

目前在X86机箱里插VCK190测试。X86、PCIe Host、Host都是指X86运行的Linux环境。Versal、Endpoint、A72都是指A72运行的Linux环境。Endpoint有时使用EP来简化。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

目前在X86机箱里插VCK190测试。X86、PCIe Host、Host都是指X86运行的Linux环境。Versal、Endpoint、A72都是指A72运行的Linux环境。Endpoint有时使用EP来简化。

Xilinx HDMI 1.4/2.0 RX的解决方案是由HDMI 1.4/2.0 Receiver Subsystem IP作为MAC和Video PHY Controller IP作为PHY组成,在板上,由外部电阻来实现TMDS level shifter,还有TMDS181作为retimer

如何实现浮点累加的PIPELINE II=1?

如果我需要修改HLS生成的RTL代码来验证一些问题,我该怎么做?

PetaLinu小技巧6则

我想在HLS之外通过命令行使用工具生成的文件来重现C/RTL协同仿真的结果。我应该使用什么文件?我怎样才能调用仿真?

MPSOC作为ZYNQ 7000的升级版,在接口方面其性能也大大增强;在一些高速数据采集的场合PS-GTR的PCIE Root Complex功能可以方便地外接WiFi模组、NVME等外设,进行数据的传输和保存

为什么Vitis HLS中的浮点累加器的精度与IEEE单精度浮点累加器不同?

本文以MRMAC IP为例,并在以太网IP的GT配置那页,选择GTM和156.25MHz时钟。

为了推断UltraRAM,你需要在所需的内部阵列上使用一个资源指令。