如何利用 ORAN IP 的例子工程做仿真

judy 在 周五, 02/18/2022 - 16:53 提交

本文将指导用户,如何使用第二种方式产生的例子工程,添加自己的数据激励,用于完成自己所需要的仿真验证

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本文将指导用户,如何使用第二种方式产生的例子工程,添加自己的数据激励,用于完成自己所需要的仿真验证

所有工具和参考设计使用2021.2。编译和测试X86主机(Host)的操作系统是CentOS 7.9.2009。测试的单板是VCK190,测试的是CPM QDMA。

提供给7系列FPGA收发器中PLL的参考时钟的质量可以极大地影响发送抖动和接收抖动容限的性能。参考时钟的抖动或相位噪声在决定这种性能方面起着重要作用--相位噪声是首选的规范方法

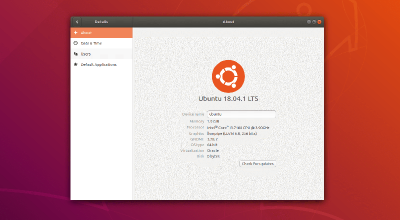

所有工具和参考设计使用2021.2。X86编译主机的操作系统是Ubuntu 18.04.6 LTS。

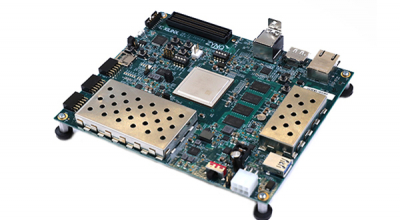

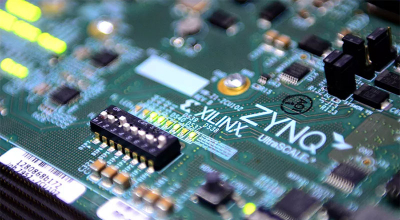

ZCU104 开发板基于Xilinx 公司Zynq UltraScale +XCZU7EV-2FFVC1156 MPSoC器件设计,支持嵌入式视觉使用案例的许多常见外设及接口

在Ubuntu 18.04下使用Vivado Jtag加载FPGA,发现找不到器件。

在解答相关问题的时候有碰到过cl_invalid_work_group_size的错误,然后通过报错信息在XRT

我们常说一句话:工欲善其事,必先利其器。作为一名FPGA工程师,我们的任务就是把某些特定的逻辑行为雕刻到FPGA芯片上,通过设计逻辑电路达到预期目的。

以前为ARM64编译软件包,直接在Makefile里指定交叉编译器、sysroot的路径,就能成功编译。

在 Zynq UltraScale+ MPSoC/RFSoC 器件中,Linux CPU Idle 默认启用。启用后,Linux 会在 CPU 内核空闲时关闭它们(与 WFI 相对)。当连接xsdb时,这可能会导致问题。