Xilinx系列FPGA 进位链延时实现简介

judy 在 周四, 11/18/2021 - 15:00 提交

FPGA芯片的三个主要资源主要包括可配置逻辑单元(CLB)、存储单元、运算单元、一流的I / O资源和布线资源等。其中,CLB在FPGA中最丰富,在7系列的FPGA中,一个CLB中有两个Slice,Slice中包含4个LUT6、3个数据选择器MUX,两个独立进位链(Carry4,Ultrascale是CARRY8)和8个主轴。这里我们主要介绍Carry4。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

FPGA芯片的三个主要资源主要包括可配置逻辑单元(CLB)、存储单元、运算单元、一流的I / O资源和布线资源等。其中,CLB在FPGA中最丰富,在7系列的FPGA中,一个CLB中有两个Slice,Slice中包含4个LUT6、3个数据选择器MUX,两个独立进位链(Carry4,Ultrascale是CARRY8)和8个主轴。这里我们主要介绍Carry4。

在FPGA的开发中,对于两个异步时钟,如果我们可以在RTL的设计中保证这两个时钟域之间的处理都是正确的,那就可以让工具不分析这两个时钟域之间的交互。

对于Xilinx的FPGA,每一片都有一个专门的ID,就像我们的身份证号一样,每个都不一样,Xilinx也形象的把这个ID叫做DNA。7系列以及之前FPGA的DNA有57bit,Ultrascale FPGA的DNA有96bit,Zynq Ultrascale+的FPGA有两个DNA,PL端一个,PS端也有一个。

分享面试中经常遇到的5个FPGA基本概念

FPGA中跨异步时钟处理的方法,是面试中经常碰到的问题,也是我们平时工作中经常会碰到的场景,对于单bit的跨异步时钟处理,我们最常用的方法就是打两拍,但这时这两级寄存器最好是放到同一个Slice中,比如下面的代码

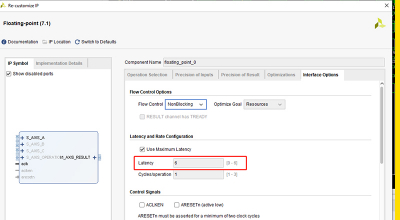

单片机的硬件串口,发送和接收完毕都有相应的标志位,例如TC(发送完成)和RXNE(接收完成)位。FPGA则不同,FPGA采用的是AXI4-Stream协议,数据送入IP核后,经过固定数量的时钟周期后,就得到运算结果,没有任何标志位表明运算完成。

本文为解决基于C++的传统定价程序带来的处理时间长、延迟高、处理速率低的问题,提出并实现了一种基于FPGA的并行流水线计算处理设计,能够完成对雪球期权的定价功能,并使用HLS开发模式对设计进行了实现。

为了使广大开发者学新学透,赛灵思开发者社区与电巢直播间特别邀请到两位赛灵思专家为大家分享Vitis及Vitis AI是如何在赛灵思异构平台(包括FPGA, SoC, Versal ACAP) 上实现嵌入式软件和加速应用。欢迎您点击关注,届时收看。

过去 20 年里,金融交易领域风起云涌:电子交易、算法、智能订单路由器持续演进;高频交易( HFT )兴起;为追求增强收益而寻找更复杂搜索策略。伴随这些趋势,金融交易指令也经历了重大变化。无论使用或编写哪种算法,在降低时延、保持性能的同时提升算法精密度和准确度,总是不变的需求。毕竟,竞争永无休止。

在对抗疾病的战斗中,药物发挥了巨大的作用。因此,每找到一方对症的新药人类就赢得了一次对疾病的斗争!但是,新药的找寻和研究从来都是极其艰难和凶险的,中国古有神农氏尝百草寻药,但最后却被断肠草毒杀。到了近代,随着对药物的研究深入到分子层级,加上计算机的辅助,新药研制加速,但是平均下来仍然需要15年左右的时间以及20亿美元的投入。