(更新)什么样的电脑配置跑Vivado FPGA综合最快?

judy 在 周三, 07/27/2022 - 10:38 提交

12代酷睿CPU在win10、11下一些问题经过的解决方法(经过实践的)

12代酷睿CPU在win10、11下一些问题经过的解决方法(经过实践的)

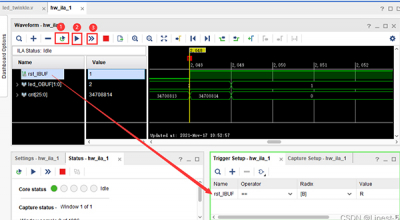

FPGA综合出来的电路都在芯片内部,基本上是没法用示波器或者逻辑分析仪器去测量信号的,所以xilinx等厂家就发明了内置的逻辑分析仪

在进行FPGA开发时,常用的代码编辑器比如Sublime,但是最近发现再Sublime中编辑的代码文字部分

之前通过发布的文章是真实的(文章是描述的)命令命令在上面的实际情况下使用的。在实现的每个子结束后打印至指定日志文件

在有些情况下,开发人员只有综合后的DCP文件和对应的约束XDC及各个IP,并没有综合之前的code,这种情况下vivado可以通过tcl脚本跑完实现并得到bit。

在用vivado开发过程中,经常vio调试核,如果要vio输出信号较多,并且信号触发顺序需要控制时,每次通过手动输入就有些麻烦

我们将介绍使用 Vivado 硬件管理器对开发板闪存进行编程的步骤。

之前很多人问我有没有好的代码可以参考,我之前一直推荐的是官方的IP参考例程/IP源码,但是不知道大家有没有看过官方的项目例程,看下下图

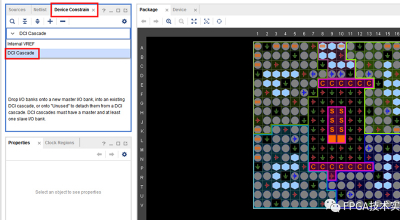

Vivado®Design Suite提供了几种可能影响I/O和时钟规划的器件规划功能。例如,FPGA配置方案、约束、配置电压方式都会影响I/O和时钟规划。

在Vivado里,可以从Block Design导出TCL脚本,保存工程。之后可以从TCL脚本恢复工程。导出的TCL脚本中,可能不包含用户IP的路径信息