百度Edgeboard FZU3 构建linux系统

judy 在 周三, 08/04/2021 - 09:43 提交

百度Edgeboard FZU3硬件平台构建和软件系统构建

百度Edgeboard FZU3硬件平台构建和软件系统构建

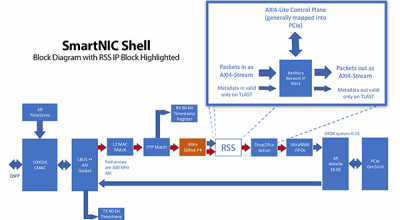

许多BittWare客户将我们基于FPGA的解决方案用于网络数据包处理,包括在网络攻击或应用代码失控的情况下捍卫服务质量。在欧洲的超大规模云提供商OVHcloud的案例中,他们的客户可以更好地免受分布式拒绝服务(DDoS)攻击。OVHcloud选择了XUP-P3R卡来构建他们最先进的过滤器,以减轻攻击,每块板卡的处理速度高达200Gbps。

近期在研究FPGA进行推理时,总结了一下三种方案,目前我了解使用FPGA进行推理还是少数,不知道大家有没有做过使用FPGA进行推理的项目,欢迎交流。

基于Vitis硬件加速平台测试用例-vector-add

本视频介绍了魔视智能最新一代遥控泊车(RPA)软硬件一体系统解决方案。该方案采用赛灵思Zu2作为主芯片,能够接4路环视摄像头、12路超声波传感器,遵循ISO26262功能安全开发,符合车规要求。本系统集成了多个神经网络,充分利用芯片优势,解决用户在泊车中的痛点,保证了系统安全可靠。

SOM (System-on-Module) 在随时可投入生产的单块印刷电路板 (PCB) 上提供嵌入式处理系统的各种核心组件,包括处理器内核、通信接口和内存模块等。有了这种模块化方法,SOM 将成为嵌入各种终端系统的理想选择,从机器人到安全摄像头,无所不包

本设计咨询涵盖如下 Versal DDRMC 设计:使用对应 LPDDR4 和 x8 或 x16 DDR4 组件接口的 DQS 字节组管脚交换所生成的设计。

本文主要包含MultiBoot的功能简介、流程介绍和工程实现几个部分的讲解。

本视频介绍宏景智驾和赛灵思一起打造的面向高等级自动驾驶系统解决方案。

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的"成本"。 但事实总是如此吗?在本文中,我们展示了一个真实的例子