最多彩的PYNQ活动—WIT Hack圆满落幕

judy 在 周一, 10/25/2021 - 09:41 提交

本次创客马拉松参赛队伍需要通过使用基于PYNQ的智能小车,在完全未知地图的情况下,通过所提供的传感器完成主办方指定的挑战。最后进入决赛的队伍,则需要根据主办方提供的传感器清单,提出自己的创意并将其实现。最终,主办方将结合竞速日成绩和决赛所展现的创意,评选出最佳表现奖、最佳创新奖和最佳新人奖,并给予现金奖励。

本次创客马拉松参赛队伍需要通过使用基于PYNQ的智能小车,在完全未知地图的情况下,通过所提供的传感器完成主办方指定的挑战。最后进入决赛的队伍,则需要根据主办方提供的传感器清单,提出自己的创意并将其实现。最终,主办方将结合竞速日成绩和决赛所展现的创意,评选出最佳表现奖、最佳创新奖和最佳新人奖,并给予现金奖励。

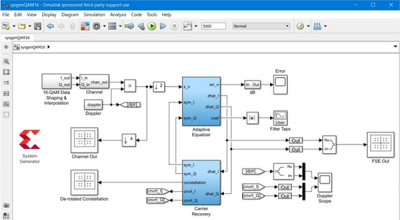

本文描述如何执行基于模型的设计,在 Simulink 环境中实现快速设计探索,并通过自动代码生成加速 Xilinx 器件的生产路径。

Vivado 仿真器支持混合语言项目文件及混合语言仿真。 这有助于您在 VHDL 设计中包含 Verilog 模块,反过来也是一样。 本文主要介绍使用 Vivado 仿真器进行混合语言仿真的一些要点。

赛灵思即将为大家带来多场线下技术交流活动,并且提供免费的KV260硬件平台现场上手实践的机会。一方面帮助已经报名和申请过硬件的参赛者们进行面对面赛事辅导;另一方面赛灵思一如既往地鼓励广大开发者和爱好者们通过研讨会进一步了解我们的最新软件开发技术与生态,更好地增强相关知识与能力。

在前面的学习中,我们知道如何根据PetaLinux BSP设计去创建一个工程,现在,我们结合Vivado设计我们自己PetaLinux系统。

Vivado 仿真器 中的实时仿真包含以下内容:

这两种类型的文件之间有什么区别?它们之间有什么关系?

赛灵思应用商店提供一个强大的平台,其可使用一个简单易用的安全数字版权管理 (DRM) 基础架构来发布、营销和销售您的解决方案,以覆盖云和本地范围内的全球客户。操作非常简单,我们的应用采用支持 DRM 的 Docker 容器封装,非常安全,可提供便捷的信用卡结算。

学习如何在 ZCU104 评估板上使用 VCU、DPU 和 PL 来构建和运行视频分析示例应用。

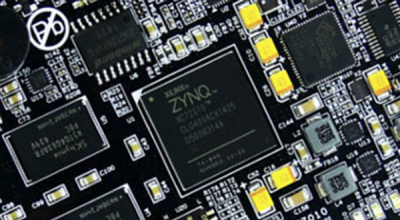

本文以XC7A35TFGG484-2这款芯片为例,采用米联客FPGA开发板,用MIG核驱动DDR3内存。FPGA外接的晶振大小为50MHz,DDR3内存的驱动频率(ddr3_ck_p和ddr3_ck_n)为400MHz。选用的DDR3内存型号为MT41K128M16,内存容量为256MB。

对于任何一项设计,要想尽可能实现最低的功率包络,都需要在设计周期早期准确估算功耗。早期估算有助于选择合适的器件、充分发挥架构优势、更改设计拓扑,以及使用不同 IP 块。在设计阶段早期妥善权衡取舍,可以帮助用户在满足规格要求的同时,将自身产品更快速推向市场。本文档旨在介绍如何根据 Versal™ ACAP 架构的描述来使用 Xilinx Power Estimator (XPE)。