ZYNQ学习之路——时序仿真

judy 在 周四, 10/28/2021 - 10:08 提交

在编写ZYNQ的FPGA逻辑代码过程中,往往需要对时序进行分析。时序信号的分析一般通常有软件仿真和在线仿真两种,本文介绍这两种方法的具体使用方法。

在编写ZYNQ的FPGA逻辑代码过程中,往往需要对时序进行分析。时序信号的分析一般通常有软件仿真和在线仿真两种,本文介绍这两种方法的具体使用方法。

近年来,“工业互联网”技术在能源电力行业得到了长足发展。随着能源互联网信息一体化、电力市场售电改革、新能源微电网与储能、智能配电终端、能源四表集抄网络、电力智能巡检等概念与政策的陆续推出,能源电力行业在基于“工业互联网”的核心指导方向下,对嵌入式解决方案在上述背景下的创新应用与升级换代的需求日益旺盛。

赛灵思今日宣布携手其 IP 及系统集成商生态系统,面向广播及专业音视频(A/V)应用提供业界首款、也是唯一一款可量产化的多媒体流式处理端节点解决方案。这些完整的解决方案具备强大的赛灵思 Zynq® UltraScale+™ EV MPSoC 和 Zynq-7000 SoC 器件

作为全球自动驾驶核心芯片的重要提供商,赛灵思认为:高性能传感器是智能驾驶的解决之道,多传感器融合是智能驾驶的必经之路。赛灵思大中华区销售副总裁唐晓蕾 2021年10月19日在上海出席中国汽车工程学会年会暨展览会 ( SAECCE 2021), 并就上述话题分享了其观点及思考,以下为其现场演讲精彩内容摘要。

Xilinx Adapt – 中国站是Xilinx Adapt 2021 线上技术大会的延伸,云集了赛灵思高层与技术专家、合作伙伴与客户,带来最新技术方案、用户案例、产品培训和应用实操。Xilinx Adapt中国站参会须知如下:

安立( Anritsu )作为一家重点从事测试测量仪器业务的企业,其目标不仅在于提供可靠、新型的测试平台,还要在实现所需功能的同时,最大限度降低功耗。借助赛灵思 Zynq® UltraScale+™ RFSoC,安立成功开发出一款高性能、可扩展的 5G NR 测试测量平台。

UltraScale SEM IP 在从 Vivado IP 目录生成和从 IP 集成器目录生成时有一定的差异。这些差异是什么呢?UltraScale SEM 打算如何在 IP 集成器中使用?

本应用说明提供了一个系统,该系统旨在通过利用每个串行千兆位收发器内的功能来取代外部压控晶体振荡器(VCXO)电路。

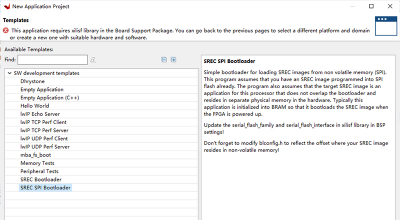

在BSP设置中,手动添加xilisf库的引用。首先,在Platform工程(这里是microblaze_test)上点击鼠标右键,选择“Open Platform Editor”命令。在Board Support Package里面,点击Modify BSP Settings按钮,勾选xilisf复选框,然后点击OK。

通过本次研讨会,了解所提供的不同层次的抽象,查看通过使用 Vitis 库启动设计的演示预演并了解您可实现的性能优势。