FPGA中加减乘除运算的注意问题

demi 在 周一, 12/09/2019 - 15:45 提交

在进行加减乘除运算时一定要注意位宽,保证足够大的位宽,防止数据溢出,如果溢出结果就会出现错误,尤其是加和乘运算,一定要计算好位宽(位宽的计算可以都取其最大值,看最大值计算后的位宽就是最大位宽,采用这个位宽数据就溢出不了)。

在进行加减乘除运算时一定要注意位宽,保证足够大的位宽,防止数据溢出,如果溢出结果就会出现错误,尤其是加和乘运算,一定要计算好位宽(位宽的计算可以都取其最大值,看最大值计算后的位宽就是最大位宽,采用这个位宽数据就溢出不了)。

有多种类型的时序违例可归类为脉冲宽度违例:最大偏差违例;最小周期违例;最大周期违例;低脉冲宽度违例;高脉冲宽度违例。

1000 位软件工程师,五年精心打磨,把用户从繁杂的硬件专业知识中解放出来的Vitis究竟有多么强大?12月17日赛灵思Vitis专场培训-厦门站,将为您一一道来。

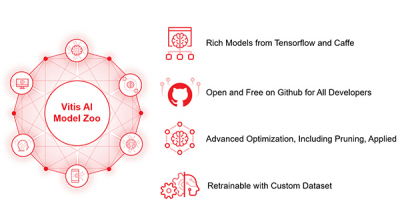

12月3-4日,Xilinx在举办了全球开发者大会,激发了近2000参会者的创新激情,现场还安排了大量的开发者上手实验。错过了大会怎么办?除了马上下载VITIS,访问Xilinx Github外,Xilinx还将在今年的FPT2019上与大家深度分享VITIS 开源加速库技术细节以及VITIS AI细节。

为支持ID路由,每个PCIE设备(端点和交换开关)中都应设置有贮存设备总线号和设备号的寄存器,复位时,该寄存器清0,每当设备在它的原级链路上检测到一个Type0配置写事务包时,它就从该TLP头标中的第8~9字节“捕获”它自己的总线号和设备号,并贮存入上述总线号和设备号寄存器。

回想一下平时我们常用的复位方式:1.首先,上电后肯定是要复位一下,不然仿真时会出现没有初值的情况;2.最好有个复位的按键,在调试时按一下复位键就可以全局复位了;3.也许是同步复位,也许是异步复位,不同的工程师可能有不同的方案。

12月3日,2019年 XDF-亚洲站在北京国家会议中心召开,在这场年度技术盛宴上,数以千计的技术工程师与专家会携广大合作伙伴、行业领导者集聚一堂,带来最新的技术解决方案与灵感洞察。

为期两天赛灵思开发者大会(XDF)亚洲站于12 月 3 日在北京国家会议中心盛大开幕。作为 FPGA 领域最重磅的年度峰会,今年的 XDF-亚洲站空前火爆,吸引了近 2000 位国内外开发者与会,数十个全球生态合作伙伴将围绕数据中心、人工智能、软件开发等七大主题发表75场高质量专题分享......

verilog参数例化——1、参数定义parameter;2、参数例化

数据中心如何加速?数百亿证券交易如何安全可靠支撑?巨大的视频图像如何实时处理?……嘉宾们在台上的分享留给开发者们太多专业上的想象空间,在这里十多家公司的数十个 demo 提供了基于赛灵思最新产品的尖端技术、创新方案和热门应用的解读......