FPGA时序约束实战篇之伪路径约束

demi 在 周四, 02/06/2020 - 09:43 提交

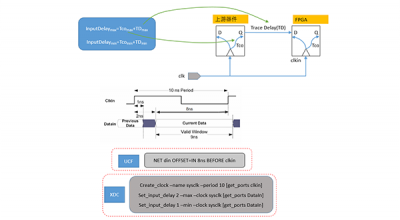

在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径。

在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径。

Xilinx的FPGA芯片中可以作为存储资源的包括LUT、BRAM、URAM。

很多FPGA初学者,都会怀疑学习FPGA有没有前途,发展前景怎么样,到底该怎样学习FPGA???各种迷茫,导致无法踏踏实实、全身心投入FPGA学习与开发工作中。下面请看看一个死磕FPGA 15年的大神给大家的肺腑之言,相信看完之后的你不在徘徊、不再犹豫、能够勇往直前。

I/O约束是必须要用的约束,又包括管脚约束和延迟约束。管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值,前者指定了管脚的位置,后者指定了管脚对应的电平标准。

赛灵思 Zynq® UltraScale+™ RFSoC 为要求最严苛的应用提供单器件 RF 转输出平台。更新的性能指标能够更加准确地衡量这些器件的直接 RF 采样功能。

十多年前,我们不会料到加速器在数据中心会这么流行。尽管它们并不普遍,但许多新的工作负载具备加速条件,并且移植工作使旧版应用程序可以卸载以提高性能。这种过渡在GPU上最为明显,但人们寄希望于FPGA将继续发展。

在证券交易领域,行情数据瞬息万变,盈利的机会转瞬即逝。“更低交易延迟”是所有金融交易追求的核心目标之一。目前国内金融行业的交易系统大部分基于传统通用CPU架构,交易提速存在瓶颈,满足不了超低时延的交易需求。

下一代基因组测序(Next Generation Sequencing ,NGS)是一个很有意义的工作,全球很多国家都在积极的参与这件事情。这需要多个学科的结合,不仅仅是生命科学,计算机科学的软件和硬件都可以在这个人类的大工程中发挥强大的力量。

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

下面讲解在vivado中怎么抓一个bit下进去后开始运行的初始事件,即startup trigger。操作起来比较复杂,一般情况下都是让要抓的事件延迟发生或者循环发生,方便调试。