【下载】Zynq UltraScale+ MPSoC 验证数据手册

demi 在 周一, 01/13/2020 - 10:57 提交

Zynq®UltraScale +™MPSoC验证知识产权(VIP)支持基于Zynq UltraScale + MPSoC的应用程序的功能仿真。 它的目标是通过模仿处理器系统(PS)-PL接口和PS逻辑的OCM / DDR存储器,来实现对可编程逻辑(PL)的功能验证。

Zynq®UltraScale +™MPSoC验证知识产权(VIP)支持基于Zynq UltraScale + MPSoC的应用程序的功能仿真。 它的目标是通过模仿处理器系统(PS)-PL接口和PS逻辑的OCM / DDR存储器,来实现对可编程逻辑(PL)的功能验证。

自动驾驶技术已成为汽车产业的最新发展方向,应用自动驾驶技术可全面提升汽车驾驶的安全性、舒适性,满足更高层次的市场需求。据市调机构 QYResearch 的预计,到 2023 年国内 ADAS 市场规模将达到 1200 亿元,未来 5 年复合增长率超过 37%。

时间:1月15日 - 17日;地点:日本东京 | 东京国际展览中心(Aomi Exhibition Hall);事件:赛灵思将现场展示多项汽车解决方案,帮助客户实现从 ADAS 到 AD(自动驾驶)的升级

随着 4G 和即将到来的 5G 时代,互联网上每天都在不断产生大量的图像和视频内容,为了保证网络环境的健康,内容提供商必须对平台产生内容进行严格的检测,避免违规违法内容流入互联网。而随着人工智能(AI)时代的到来,图像智能处理系统开始逐渐替代基础的审核人员。

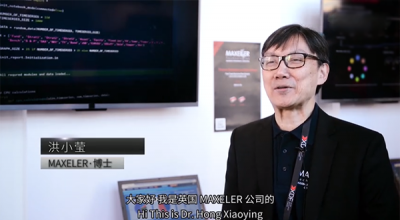

在 2019 XDF(赛灵思开发者大会)上, Maxeler 公司洪小莹博士为大家现场展示了其基于 Alveo 加速卡的 CVA Calculation (信用风险评估调整)的方案。

大数据时代呼唤算力的革命,未来的“计算”将会是什么样?作为引领下一代自适应 AI 技术的全球领导者,赛灵思如何规划和布局?现在真的是软件开发者的天下了吗?

xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

Zynq中断大致可分为三个部分,第一部分为SGI,软件生成的中断,共16个端口;第二部分为PPI,CPU私有外设中断,有5个;第三部分为SPI,共享外设中断,来自于44个PS端的IO外设以及16个PL端的中断。中间部分为GIC,也即中断控制器,用于对中断进行使能、关闭、掩码、设置优先等。

多周期路径,我们一般按照以下4个步骤来约束:带有使能的数据;两个有数据交互的时钟之间存在相位差;存在快时钟到慢时钟的路径;存在慢时钟到快时钟的路径。

Zynq®UltraScale +™MPSoC器件是Zynq®-7000SoC器件的后继产品。 它提供了64位处理器的可扩展性,同时将实时控制与用于图形,视频,波形和数据包处理的软引擎和硬引擎相结合。