ZC706评估板IBERT误码率测试和眼图扫描

judy 在 周三, 03/10/2021 - 14:40 提交

IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPGA高速串行接口比特误码率性能的工具,最常用在GT高速串行收发器测试:

(1)基于PRBS模块的误码率测试;

(2)测量眼图;

IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPGA高速串行接口比特误码率性能的工具,最常用在GT高速串行收发器测试:

(1)基于PRBS模块的误码率测试;

(2)测量眼图;

ZC706中,MAC 控制器与 PHY 通过 RGMII(Reduced Gigabit Media Independent Interface)接口进行连接,实现千兆网。

在Vivado使用过程中,会碰到如下情况:设计代码已经编写完成,且仿真、综合或实现中的某一步骤已经通过,不需要再修改。此时可能需要添加一些注释代码,或者调整代码的格式,而任何修改都会导致状态更改为“Out of date”,提示用户更新设计。如何才能在不重新运行综合或实现的情况下解决这个问题?

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?比如针对输入的异步复位信号rst,使用本地时钟clk将其同步化以后得到一个新的复位信号sys_rst,当使用sys_rst时,是将sys_rst作为同步复位信号还是异步复位信号?

vivado建立的工程经常会出现版本升级而导致的IP核锁定情况,本文以vivado 2019.2的版本打开旧版本为例,介绍两种更新方法

总结了20个DDR3和FPGA部分的设计规范

在Xilinx FPGA中实现的设计不需要插入全局复位网络。对于绝大多数设计,所有触发器和RAM的上电后的初始化状态比任何的逻辑复位都要全面,不需要为了仿真而插入复位,因为没有任何东西是未定义的

FPGA 融合了 ASIC 和基于处理器的系统的最大优势,它能够提供硬件定时的速度和稳定性,且无需类似自定制 ASIC 设计的巨额前期费用的大规模投入。但是和所有的数字电路一样,FPGA 电路中也存在毛刺问题。它的出现会影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

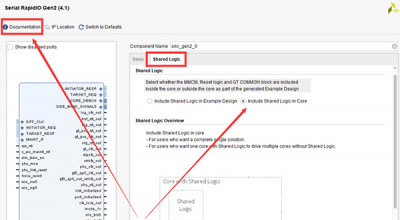

这里以Xilinx为例,在Vivado中使用SRIO高速串行协议的IP演示如何使用官方例程和手册进行快速使用,在仔细阅读参考官方例程后进行一些修改就可以应用在实际项目中。

源语(Primitives)-Xilinx库中最简单的设计元素。Primitives 基元是设计元素“原子”。Xilinx原语的示例包括简单缓冲区BUF和带有时钟使能和清除功能的D触发器FDCE。