让ARM穿上FPGA的马甲,会演一出什么好戏?

judy 在 周五, 11/06/2020 - 09:32 提交

随着赛灵思公司推出28nm Zynq-7000 All Programmable SoC以后,FPGA在工业应用大有加速之势,赛灵思工业级客户增长非常迅猛,其数量远超通信客户。赛灵思Zynq器件在智能化工业自动化领域大显身手,它将给工业应用带来哪些深刻变革?

随着赛灵思公司推出28nm Zynq-7000 All Programmable SoC以后,FPGA在工业应用大有加速之势,赛灵思工业级客户增长非常迅猛,其数量远超通信客户。赛灵思Zynq器件在智能化工业自动化领域大显身手,它将给工业应用带来哪些深刻变革?

在《AXI-Lite 自定义IP》章节基础上,添加ila\vio等调试ip,完成后的BD如下图:加载到SDK,并且在Vivado中连接到开发板。

Trigger Setup,点击“+”,选择 AXI_WVALID,双击添加。设置 Radix 为 B,触发条件 Value 为 1。

最近群里有很多人遇到上述的情况,一直觉得不可思议,以前没有遇到这种情况,如果是很常见的情况,那官网一定有人反馈,如果是极特别的情况,那么也就只能按照BUG处理了。很幸运,官网有很多人反馈类似的问题,先把问题和解决方式放出来:

FPGA (Field Programmable Gate Aray,现场可编程门阵列)是一种可通过重新编程来实现用户所需逻辑电路的半导体器件。为了便于大家理解FPGA的设计和结构,我们先来简要介绍一些逻辑电路的基础知识。

通过嵌入式软核或者硬核通过AXI_Lite接口(Master)控制FPGA端引脚的GPIO。按照AXI互联机制我们知道,我们的自定义IP是通过AXI_Interconnect连接到Master端,整体的框图也比较简单,为了验证方便我们只按照红色线路径进行测试。

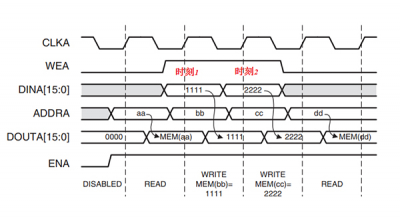

当我们调用RAMO的IP时,无论是单端口还是双端口模式,都会有个选项,可能很多人都没注意过这个选项,记得毕业季去华为面试的时候,还问过我这个问题,当时也是没答上来。后来也发现很多面试官都喜欢问这个问题,今天我们就来讲一下。

本文将从代码风格,时序修正,工程设置等几个方面介绍本人的实践经验,希望让各位初学者快速提高,也希望FPGAer能给出宝贵建议。

今天想和大家一起聊聊FPGA的IO。先说说我当年入门的经历吧。国内的大学有FPGA开发条件的实验室并不太多,当年大学的那帮同学有的做ARM,有的做linux,很少有人做FPGA,当时学FPGA仅仅是由于非常渴望的好奇心。所以,在淘宝买了一块开发板,就开始了自己的FPGA之路。

对于使用AXI总线,最开始肯定要了解顶层接口定义,这样才能针对顶层接口进行调用和例化,打开axi_lite_v1_0.v文件,第一段就是顶层的接口定义:

要看到AXI-Lite的源码,我们先要自定义一个AXI-Lite的IP,新建工程之后,选择,菜单栏->Tools->Creat and Package IP