【Vivado那些事】Vivado下头文件使用注意事项

judy 在 周四, 12/17/2020 - 11:17 提交

并不局限于Vivado一种EDA。头文件主要使用“文件包括”处理,所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog语言提供了`include命令用来实现"文件包含"的操作。

并不局限于Vivado一种EDA。头文件主要使用“文件包括”处理,所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog语言提供了`include命令用来实现"文件包含"的操作。

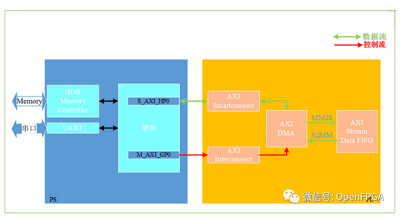

DMA中断实例化函数,将要配置的DMA信息先lookupConfig再进行CfgInitialize,DMA采用块模式(Block mode),如果是Sg模式,则配置失败。定时器初始化函数,传入参数有定时器结构、加载值,设备ID。

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

完成Implementation后,在Vivado IDE左侧的Flow Navigator点击Open Implemented Design,然后点击report_utilization。

Xilinx-7系列FPGA主要包括:Spartan®-7、Artix®-7、Kintex®-7、Virtex®-7。其性能、密度、价格也随着系列的不同而提升。和前几代FPGA产品不同的是,7系列FPGA采用的是统一的28nm设计架构,客户在不同子系列的使用方式上是统一的,消除了不同子系列切换使用带来的不便。当然Kintex®-7、Virtex®-7两个系列后续还有20nm和16nm设计架构。

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。

增加一个AXIDMA章节,这部分内容是很多例程的基础,难度不大但是也不小,需要彻底理解整个运行机制。

有的时候需要查找一些官网的例程进行学习和参考,但是总感觉无从下手,今天就教大家怎么利用官网和Vivado的Documention进行相关的操作。

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

区别于传统的一根信号线一根地线的做法,差分传输在两根线上都传输信号,这两个信号的振幅相同,相位相反,在这两根线上的传输的信号就是差分信号。信号接收端通过比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。