基于Xilinx的时序分析与约束(8)----关于时序路径、时钟悲观度和建立时间/保持时间的一些问题

judy 在 周二, 01/17/2023 - 10:25 提交

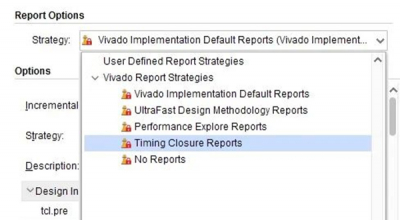

最近研究vivado里的时序分析路径时,发现了3个很有意思的问题

最近研究vivado里的时序分析路径时,发现了3个很有意思的问题

本章介绍7系列FPGA的配电系统(PDS)

本文介绍一些计数器的常用方法和注意点

UltraScale器件中时钟管理模块(CMT)包含mixed-mode clock manager (MMCM) 和phase-locked loops (PLLs)

本文讨论当前PCB技术的基础,重点是物理结构和常见假设

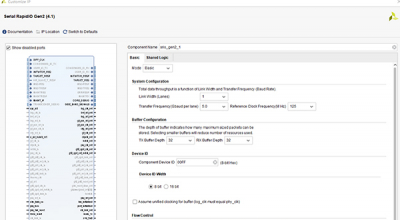

因为工作原因,需要对rapidio 的协议进行了解,在xilinx的IP核中,是对应着Serial RapidIO Gen2 这个IP核

串并、并串转化也是FPGA设计中常见的基本问题,相对来说比较简单

为了更精确地进行时序分析,设计者还必须设定一些与运行环境相关的可预测变量和随机变量

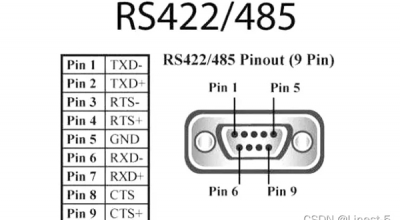

RS-232接口符合电子工业联盟(EIA)建立的串行数据通信接口标准

首先,从理论上讲,Hold Time违例,是因为时钟绕的太远,到达时间太晚