Xilinx时钟组件的原语

judy 在 周二, 07/05/2022 - 10:00 提交

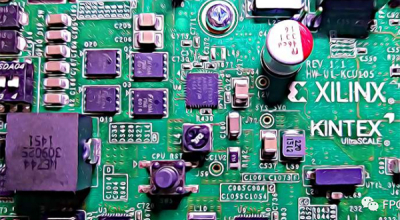

xilinx提供了丰富的原语,可以将之看成FPGA开发可以使用的库函数,原语在FPGA中具有与之对应的硬件逻辑单元,但也注意,不同的FPGA的原语可能会有所不同

xilinx提供了丰富的原语,可以将之看成FPGA开发可以使用的库函数,原语在FPGA中具有与之对应的硬件逻辑单元,但也注意,不同的FPGA的原语可能会有所不同

我们今天要学习的正是由BRAM资源构成的RAM IP核----Block Memory Generator。

我们在设计外设和Xilinx 7系列FPGA互联时,经常会用到LVDS接口。如何正确的保证器件之间的互联呢?本博文整理了Xilinx官方相关技术问答

在用vivado开发过程中,经常vio调试核,如果要vio输出信号较多,并且信号触发顺序需要控制时,每次通过手动输入就有些麻烦

Block_RAM应该是每个FPGA开发者经常遇到的,其作为一种固定资源存在于FPGA中,针对xilinx的BRAM,正常通过vivado的IP Core Generator得到

本文将告诉你:对于小型设计,要如何编写一个高效率的testbench。

之前很早就听说了FSMC接口用于MCU与FPGA之间的通讯。最近使用的一款MCU与FPGA之间通讯,FPGA模拟成NAND Flash作为Memory让MCU读写

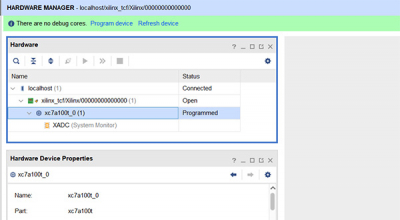

我们将介绍使用 Vivado 硬件管理器对开发板闪存进行编程的步骤。

CLB实际上是四种基本元素的集合----查找表LUT,进位链CARRY4,多路选择器Multiplexer以及存储单元FF。

Xilinx Platform Cable USB II无论是官方的DLC10,还是第三方的DLC9均无法 识别,表现为以下几种