FPGA AMBA APB Bridge

judy 在 周一, 06/20/2022 - 10:15 提交

APB总线作为AMBA体系中低速的总线,通常用于CPU访问或者配置低速外设的寄存器。APB总线的功能与AXI-Lite总线相似

APB总线作为AMBA体系中低速的总线,通常用于CPU访问或者配置低速外设的寄存器。APB总线的功能与AXI-Lite总线相似

在数字电路中存储单元有两种,一种是触发器,一种是锁存器。它们两者最大的区别是:前者通过时钟沿到来改变存储的输出状态,后者是通过电平变换来改变存储的输出状态。

FPGA与STM32等嵌入式开发最大的一个优点就是,可以在时序仿真阶段验证超过90%的功能,发现90%的问题

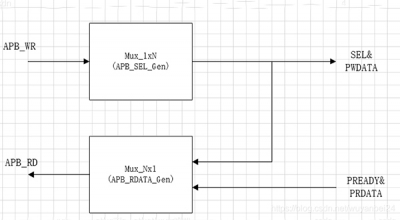

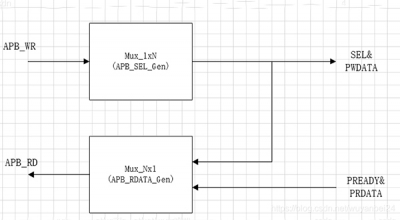

多路选择器MUX是一个多输入、单输出的组合逻辑电路,一个n输入的多路选择器就是一个n路的数字开关,可以根据通道选择控制信号的不同

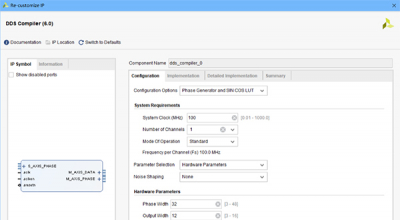

随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。

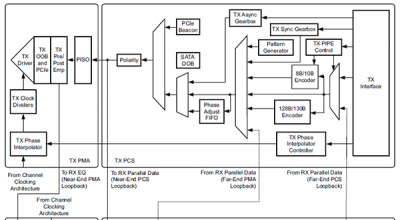

长时间没有做高速相关的FPGA单板开发,一直停留在GTX和GTP的时代,是时候梳理一下,从Xilinx的7系列到目前的ultrascale系列

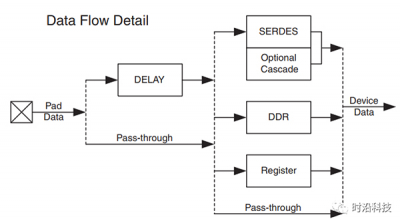

本文主要针对Xilinx SelectIO IP的GUI(图形用户界面),对每个参数进行详细解释,理解其中的内涵,快速完成驱动设计。

时钟门控是一种很好理解的功率优化技术,用于ASIC和FPGA设计,以消除不必要的开关行为。这种方法通常需要设计者在他们的RTL代码中添加少量的逻辑来禁用或取消不必要的活动时序单元--例如寄存器

记得刚接触FPGA的时候,总能看见类似这样的一句话----FPGA是基于查找表LUT的可编程逻辑器件。FPGA常常被人比作“数字积木”,就是因为底层资源的丰富和灵活,要做任何“玩具”

用过单片机的朋友都知道,单片机芯片内部都有一串序列号,比如STM32,称之为Unique device ID,是一个96Bit的只读数据。和单片机一样,FPGA芯片内部同样也有ID